Obsah

2. Struktura grafického systému Pixel-Planes

3. Technické parametry grafického systému Pixel-Planes

4. Grafický subsystém Reality Engine

5. Moduly grafického subsystému Reality Engine – procesor příkazů

6. Moduly grafického subsystému Reality Engine – Geometry Engine

7. Obsah následující části seriálu

1. Architektura Pixel-Planes

Prvním grafickým systémem, který si v dnešní části seriálu o architekturách počítačů popíšeme, je grafický systém nazvaný Pixel-Planes. Jedná se o speciální typ grafického akcelerátoru určeného především pro výzkumné účely (z komerčního hlediska se z několika dále uvedených důvodů jedná o nepříliš zajímavou architekturu), který se od ostatních dříve popsaných grafických akcelerátorů odlišuje především v tom, že jeho tvůrci nepoužili klasický vykreslovací řetězec (dnes představovaný grafickým procesorem – GPU) napojený na framebuffer a texturovací paměť. Namísto toho je framebuffer, který obvykle bývá představován pamětí SRAM, DRAM či v některých případech i speciální dvoubránovou pamětí, v architektuře Pixel-Planes rozdělen na jednotlivé pixely, přičemž každému pixelu je přiřazen samostatný, poměrně jednoduchý pixelový procesor (tj. aritmeticko-logická jednotka s přídavnými obvody) vybavený malou pamětí s kapacitou pouhých 72 bitů, v níž mohou být uloženy všechny důležité informace o pixelu (přesněji řečeno fragmentu, protože se může jednat o pixel s přiřazenou hloubkou i dalšími atributy).

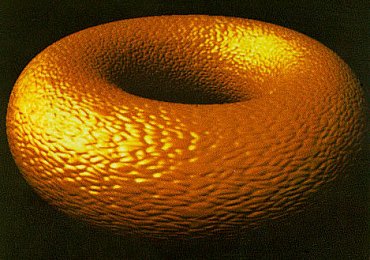

Obrázek 1: Toroid, při jehož vykreslování byl použit algoritmus bump mappingu. Tento algoritmus je založen na modulaci normálových vektorů (jedná se o normálové vektory přiřazené polygonům nebo o vektory přiřazené ke společným vrcholům několika polygonů) na základě hodnoty uložené v textuře či hodnoty vypočtené z funkce procedurální textury.

Jedná se tedy o architekturu, která pracuje zcela jiným způsobem než většina ostatních grafických akcelerátorů, což mj. znamená, že se při vykreslování používají i v mnoha ohledech odlišné algoritmy. Filozofie této architektury totiž vychází z masivního paralelismu, při němž se současně mohou zpracovávat všechny pixely ve framebufferu, ovšem prováděné operace jsou velmi jednoduché (délka trvání jedné složitější operace je rovna cca 20–30 cyklům, protože procesor zpracovává data po jednotlivých bitech). Naproti tomu prakticky všechny moderní grafické akcelerátory sice taktéž používají paralelní zpracování dat, ale v mnohem menší míře – vysoký výpočetní výkon dnešních akcelerátorů je dosažen především rozdělením celého rasterizačního řetězce do mnoha řezů, takže vzniká grafická pipeline, která dokáže v jednom kroku současně provést velké množství operací, ovšem každá operace je provedena v jiné části rasterizačního řetězce – viz následující obrázek, na němž jsou zobrazeny operace, které se provádí v rasterizačním řetězci typického soudobého grafického akcelerátoru.

Obrázek 2: Operace s fragmenty prováděné při rasterizaci trojúhelníků či obecnějších konvexních polygonů na moderním grafickém akcelerátoru.

2. Struktura grafického systému Pixel-Planes

Nejdůležitější částí architektury Pixel-Planes jsou specializované zákaznické čipy, z nichž každý obsahuje 128 pixelových procesorů, přičemž pro každý pixel je vyhrazeno 72 bitů v paměti instalované na čipu (každý pixelový procesor přistupuje přímo ke „svým“ 72 bitům). Na třetím obrázku umístěném pod tímto odstavcem je zobrazeno zjednodušené schéma části framebufferu s rozlišením 8×8 pixelů. Můžeme zde vidět, že ke každému pixelu je skutečně přiřazen jednoduchý pixelový procesor s jednobitovou aritmeticko-logickou jednotkou, který může přistupovat k paměti o kapacitě 72 bitů (celková kapacita paměti na jednom zákaznickém čipu je rovna 128×72=9216 bitům, tj. 1152 bajtům). Data se do každého procesoru posílají a následně zpracovávají sériově, tj. každý procesor přijme v každém taktu pouze jediný bit informace. Vzhledem k tomu, že všechny procesory na čipu pracují paralelně, jsou na každém čipu architektury Pixel-Planes implementovány sběrnice o šířce 128 bitů (šířka těchto sběrnic tedy odpovídá celkovému počtu pixelových procesorů umístěných na jednom čipu).

Obrázek 3: Zjednodušené schéma části framebufferu architektury Pixel-Planes s rozlišením 8×8 pixelů.

Při rasterizaci (vykreslování objektů) se pro každý zpracovávaný pixel provádí výpočet lineárních výrazů majících tvar F(x,y) = A*x + B*y + C, kde x a y jsou souřadnice pixelu a A, B a C jsou koeficienty zvolené podle toho, jaká operace se má provádět (může se například jednat o operaci rasterizaci trojúhelníka, výplň obdélníkové oblasti vzorkem, výpočet barev pixelů na základě algoritmu Gouraudova stínování atd.). Výsledná hodnota vzniklá vyhodnocením lineárního výrazu může být použita pro obarvení pixelu, test hloubky pixelu (fragmentu) atd. To, jaká operace se skutečně provede, záleží na algoritmu, který systém Pixel-Planes v daný okamžik provádí. Ovšem kdyby každý procesor musel samostatně provádět celý výpočet výše uvedeného lineárního výrazu, bylo by to neefektivní, protože většina výpočtů by se zbytečně duplikovala a navíc by musely být tyto procesory mnohem složitější než ty, které byly ve skutečnosti v architektuře Pixel-Planes použity (na tomto místě je vhodné si uvědomit, že pro framebuffery běžných rozlišení se zde bavíme například o čtvrt milionech procesorů, takže každé nadbytečné hradlo by celý grafický akcelerátor mohlo dosti podstatným způsobem prodražit).

Namísto toho je v architektuře Pixel-Planes kromě jednobitových ALU přiřazených každému pixelu implementována i výpočetní struktura nazvaná strom lineárních výrazů, která pro každý pixel (přesněji pro každý pixelový procesor) předpočítá hodnoty A×x+C a B×y, které se následně každému pixelovému procesoru pošlou sériovým protokolem (v každém taktu jeden bit). Pixelový procesor posléze obě hodnoty sečte a provede s výsledkem F požadovanou operaci, například její zápis do své paměti (tím může dojít například ke změně barvy pixelu nebo jeho hloubky). Poznamenejme, že kromě zde popisované architektury Pixel-Planes (verze 4) byla navržena i její modernější verze Pixel-Planes 5, v níž se již kromě lineárních výrazů mohou vyhodnocovat i výrazy obsahující druhé mocniny souřadnic x a y. Pro Pixel-Planes 5 je tak například snadné implementovat algoritmus vykreslování koulí, některých typů spline ploch, složitější osvětlovací modely atd.

3. Technické parametry grafického systému Pixel-Planes

Grafický akcelerátor Pixel-Planes obsahoval celkem 262 144 pixelových procesorů s přiřazenou 72 bitovou pamětí, pomocí nichž byl vytvořen framebuffer s rozlišením 512×512 pixelů (512×512=262144). Vzhledem k tomu, že na jeden zákaznický čip bylo možné umístit 128 těchto procesorů (jedná se o technologii roku 1986, kdy tato architektura vznikla), bylo nutné pro konstrukci celého akcelerátoru Pixel-Planes použít celkem 2048 těchto čipů (262144/128=2048), což je jeden z důvodů, proč se neuvažovalo o jeho komerčním nasazení, i když výkonnost této architektury byla na dobu vzniku více než dobrá – za jednu sekundu bylo možné vykreslit až 40 tisíc trojúhelníků vystínovaných pomocí Gouraudova stínování, přičemž tyto trojúhelníky mohly mít libovolnou velikost (nezávislost rychlosti vykreslování na velikosti vykreslovaných obrazců je ostatně jedna z nejzajímavějších vlastností této architektury). Jak již bylo řečeno v předchozích odstavcích, jsou současné grafické akcelerátory vystavěny nad běžným framebufferem (statickou či dynamickou pamětí) a výkonným GPU.

4. Grafický subsystém Reality Engine

V předchozí části tohoto seriálu jsme si popsali architekturu serverů Onyx 2 spolu s jejich grafickým subsystémem Infinite Reality. Firma SGI ovšem v mnoha svých počítačích využívala i odlišné typy grafických subsystémů. Jednou z alternativ (a částečně i předchůdcem) grafického subsystému Infinite Reality je architektura Reality Engine, kterou si popíšeme v následujícím textu. Tato architektura se v některých ohledech podobá výše popsané architektuře Pixel-Planes, zejména způsobem zapojení procesorů specializovaných na provádění operací s fragmenty uloženými ve framebufferu. Na čtvrtém obrázku umístěném pod tímto odstavcem jsou zobrazeny jednotlivé funkční bloky, ze kterých se grafický subsystém Reality Engine skládá. Na obrázku můžeme vidět, že je celý subsystém sestaven z několika samostatných desek nazvaných geometry board, raster memory board a display generator board (existuje více konfigurací těchto desek, kterých může být 3, 4 nebo 6).

Obrázek 4: Funkční bloky grafického subsystému Reality Engine.

Na první desce grafického subsystému Reality Engine se nachází jeden procesor příkazů (Command Processor) a několik bloků určených pro zpracování geometrických informací (Geometry Engine(s)). Přesný počet těchto bloků se liší v závislosti na tom, zda se jedná o původní verzi Reality Engine nebo o její inovovanou variantu nazvanou Reality Engine2. Na druhé desce, kterých může být v počítači nainstalováno více (jejich vzájemné propojení je realizováno speciální sběrnicí Triangle Bus), se nachází generátory fragmentů (Fragment Generator(s)) provádějící rasterizaci trojúhelníků a taktéž pole procesorů určených pro provádění operací s jednotlivými pixely (Image Engine(s)). Poslední deska slouží pro zpracování výsledného rastrového obrazu a pro generování video signálu určeného pro monitory popř. pro další vhodná grafická výstupní zařízení. V následujících kapitolách si funkce jednotlivých bloků, ze kterých se Reality Engine skládá, popíšeme do větších podrobností.

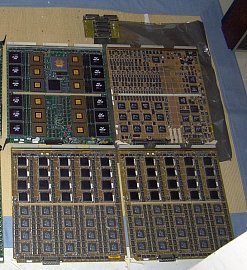

Obrázek 5: Čtyři desky, ze kterých se skládá grafický subsystém Reality Engine. Existuje i méně výkonná konfigurace se třemi deskami a naopak výkonnější konfigurace obsahující šest desek.

5. Moduly grafického subsystému Reality Engine – procesor příkazů

První deskou, z níž se grafický subsystém Reality Engine skládá, je deska obsahující procesor příkazů a sadu modulů nazvaných Geometry Engine. Procesor příkazů (Command Processor) slouží k postupnému načítání příkazů, které jsou uloženy do fronty (FIFO). Jedná se o příkazy, které odpovídají funkcím grafické knihovny OpenGL. V případě, že se jedná o příkaz, který mění parametry vykreslování (například nastavení transformační či projekční matice, změna parametrů osvětlovacího modelu atd.), je tento příkaz příkazovým procesorem distribuován ke všem modulům Geometry Engine.

Obrázek 6: Schéma systému Reality Engine se zvýrazněnou deskou geometry board.

Pokud se naopak jedná například o příkaz odpovídající funkci glColor*() (barva vrcholu), glVertex*() (souřadnice vrcholu) apod., je tento příkaz poslán pouze do jednoho modulu Geometry Engine, přičemž si procesor příkazů sám pamatuje, kterému modulu byl tento příkaz zaslán, protože všechny informace o jednom vrcholu (barva, textura, souřadnice v textuře, pozice vrcholu v prostoru) musí být poslány do téhož modulu Geometry Engine. Příkazový procesor taktéž automaticky rozkládá delší sekvenci segmentů polyčar (line strip, line loop) či dlouhé pruhy trojúhelníků (triangle strip) na menší části, aby došlo k co nejlepšímu vytížení všech modulů Geometry Engine (jedná se o klasický load balancing).

Obrázek 7: Deska obsahující procesor příkazů a osm procesorů Intel 860 spolu s dalšími obvody zajišťujícími vzájemnou komunikaci všech čipů.

6. Moduly grafického subsystému Reality Engine – Geometry Engine

Za procesorem příkazů se nachází řada modulů Geometry Engine, jichž může být podle požadovaného výpočetního výkonu nainstalováno 6, 8 nebo 12. Každý modul Geometry Engine je sestaven z procesorů Intel i860XP, jejichž základní technické parametry jsme si již popsali v předchozích částech tohoto seriálu. Připomeňme si jen, že se jedná o mikroprocesor firmy Intel z roku 1989, který má architekturu RISC a instrukční sadu typu VLIW (v jednom instrukčním slově je tedy zakódováno větší množství operací, přičemž každá z těchto operací je určená pro jinou jednotku na čipu, což zjednodušuje návrh procesoru, který nemusí obsahovat složitý řadič, který by se staral o přidělování jednotek jednotlivým instrukcím). V podstatě se jedná o (na dobu vzniku velmi výkonný) signálový procesor podporující celočíselné operace i operace s hodnotami uloženými v systému plovoucí řádové čárky, který je navíc vybavený jednotkou specializovanou pro provádění některých grafických operací.

Obrázek 8: Mikroprocesor Intel i860, který je nedílnou součástí grafického subsystému Reality Engine.

V každém modulu Geometry Engine je prováděna transformace souřadnic vrcholů i jejich normálových vektorů na základě zadané transformační matice, odstranění těch polygonů, které jsou odvrácené od uživatele, odstranění polygonů, jež se nachází mimo viditelnou část prostoru (jedná se o podprostor ve tvaru komolého jehlanu) a taktéž transformace souřadnic v prostoru textur. Transformované polygony jsou navíc rozděleny na trojúhelníky, které jsou následně poslány na sběrnici nazvanou Triangle Bus.

Obrázek 9: Blokové schéma jednoho modulu Geometry Engine. Zde můžeme vidět, že se tento uzel skládá z procesoru Intel i860XP, paměťového čipu a taktéž zákaznického obvodu určeného pro komunikaci s okolními čipy. Viz též obrázek číslo 7, na němž je fotka celé desky s osmi moduly Geometry Engine.

7. Obsah následující části seriálu

V následující části seriálu o architektuře počítačů dokončíme popis grafického subsystému Reality Engine. Řekneme si, jakým způsobem jsou transformované trojúhelníky předávány modulům vytvářejícím jednotlivé fragmenty (vzhledem k tomu, že je každý trojúhelník poslán do 5, 10 či 20 těchto modulů, musí každý Fragment Generator zpracovat pouze 20%, 10% či pouze jen 5% fragmentů každého trojúhelníku, což samozřejmě představuje velmi významné urychlení vykreslování, a to i v případě, že je využit antialiasing, který celé vykreslování prostorové scény komplikuje) a jak pracuje pole modulů nazvaných Image Engine(s).

Obrázek 10: Druhá deska, z níž se skládá grafický subsystém Reality Engine. Na této desce jsou umístěny generátory fragmentů sloužící k vlastní rasterizaci objektů a taktéž pole modulů Image Engine(s) určených pro provádění operací nad jednotlivými fragmenty.

8. Literatura

- Fuchs, H., Goldfeather, J., Hultquist, J., Spach, S., Austin, J., Brooks, F., Eyles, J., and Poulton, J.,:

„Fast Spheres, Shadows, Textures, Transparencies, and Image Enhancements in Pixel-Planes“

Computer Graphics (SIGGRAPH '85 Conference Proceedings), Vol. 19, No. 3, July, 1985, pp 111–120. - Fuchs, H., Poulton, J., Eyles, J., Greer, T., Goldfeather, J., Ellsworth, D., Molnar, S., Turk, G., and Israel, L.,:

„A Heterogeneous Multiprocessor Graphics System Using Processor-Enhanced Memories“

Computer Graphics (Proceedings of SIGGRAPH '89), Vol. 23, No. 3, pp 79–88. - Poulton, J.,:

„Building Microelectronic Systems in a University Environment“

Proceedings of the 1991 Conference on Advanced Research in VLSI, (invited presentation) UC-Santa Cruz, March 25–27, 1991, pages 387–400. - Andries van Dam, Steven K. Feiner, John F. Hughes:

„Computer Graphics: Principles and Practice in C“

(2nd Edition) - Henry Styles and Wayne Luk:

„Customising Graphics Applications: Techniques and Programming Interface“

Department of Computing, Imperial College, London, England - Akeley, Kurt: „RealityEngine Graphics“

Proceedings of SIGGRAPH '93, pp. 109–116.

9. Odkazy na Internetu

- Pixel-Planes Project

http://www.cs.unc.edu/~pxfl/history.html - Pixel-Plane 5

http://www.cs.sunysb.edu/~vislab/papers/pvr/rpe/node27.html - Tiled rendering

http://en.wikipedia.org/wiki/Tiled_rendering - PowerVR

http://en.wikipedia.org/wiki/PowerVR - High-Performance Graphics Architectures: The Pixel-Planes Group

http://www.cs.unc.edu/~pxfl/pxpl-summary.html - Reality Engine

http://en.wikipedia.org/wiki/RealityEngine - Geometry pipelines

http://en.wikipedia.org/wiki/Geometry_Engine - SGIstuff : Hardware : Graphics : RealityEngine

http://old.sgistuff.net/hardware/graphics/reality.php - Onyx2 Technical Specification

http://vintagecomputers.info/onyx2/tech_specs.html - Video Technology Magazine – various graphics resolutions

http://www.videotechnology.com/0904/formats.html - Ultra XGA (Ultra eXtended Graphics Array)

http://www.pcmag.com/encyclopedia_term/0,2542,t=UXGA&i=53603,00.asp - UXGA (Ultra eXtended Graphics Array)

http://en.wikipedia.org/wiki/UXGA - WUXGA (Widescreen Ultra eXtended Graphics Array)

http://en.wikipedia.org/wiki/WUXGA - Video Standards (Graphics resolutions)

http://en.wikipedia.org/wiki/File:Vector_Video_Standards2.svg - The MIPS R10000 Superscalar Microprocessor (článek dostupný členům ACM)

http://portal.acm.org/citation.cfm?id=623999 - Glide API

http://en.wikipedia.org/wiki/Glide_API - Scientific Application of OpenGL Vizserver within High Performance Computing

http://www.ukhec.ac.uk/publications/reports/vizserver_casestudy_dec02.pdf - Amdahl's law

http://en.wikipedia.org/wiki/Amdahl%27s_law - NUMA: Frequently Asked Questions

http://lse.sourceforge.net/numa/faq/ - NUMA (Numa Support in Linux)

http://oss.sgi.com/projects/numa/ - Symmetric multiprocessing

http://en.wikipedia.org/wiki/Symmetric_multiprocessing - Non-Uniform Memory Access

http://en.wikipedia.org/wiki/Non-Uniform_Memory_Access - Northbridge (computing)

http://en.wikipedia.org/wiki/Northbridge_(computing) - Southbridge (computing)

http://en.wikipedia.org/wiki/Southbridge_(computing) - Carrier sense multiple access with collision detection

http://en.wikipedia.org/wiki/Carrier_sense_multiple_access_with_collision_detection - Intel i740

http://en.wikipedia.org/wiki/Intel740 - Intel i740 Datasheet

ftp://download.intel.com/support/graphics/intel740/29061902.pdf - Intel740™ Graphics Accelerator P854 Hardware

ftp://download.intel.com/support/graphics/intel740/29062202.pdf - S3 Savage

http://en.wikipedia.org/wiki/S3_Savage - Savage (S3)

http://www.economy-point.org/s/savage-s3.html - 3dfx Interactive

http://en.wikipedia.org/wiki/3dfx_Voodoo_Graphics - Visualization Tools and Environments for Very Large Data

http://ditwww.epfl.ch/SIC/SA/publications/SCR00/scr12-page9.html - Intel 860@cpu-collection

http://www.cpu-collection.de/?l0=co&l1=Intel&l2=i860 - S3 Graphics

http://www.s3graphics.com/en/index.aspx - TSENG ET6000 Performance Page

http://dani75.tripod.com/TSENG.htm - Tseng Labs Ships ET6000 Advanced Graphics Chip, Announces Additional Manufacturing Sources

http://www.encyclopedia.com/doc/1G1–18088868.html - CyberMax chooses Tseng Labs' ET6000 Graphics and Video Controller for Max and ProMax Series PCs

http://findarticles.com/p/articles/mi_m0EIN/is_1996_Oct9/ai_18754932/ - Intel i860

http://en.wikipedia.org/wiki/Intel860 - Intel i860 64-Bit Microprocessor

http://www.microprocessor.sscc.ru/i860.html - 25 Microchips That Shook the World

http://www.synbio.org.uk/scientific-computing-news/1351.html - Sprite (computer graphics)

http://en.wikipedia.org/wiki/Sprite_(computer_graphics) - Sprite (počítačová grafika)

http://cs.wikipedia.org/wiki/Sprite_(počítačová_grafika) - Wikipedia: Video Display Controller

http://en.wikipedia.org/wiki/Video_Display_Controller - 3dfx Voodoo1 PCI

http://www.v3info.de/english/html/v1.shtml - Glide 2.2 Programming Guide

http://www.gamers.org/dEngine/xf3D/glide/glidepgm.htm - OpenGL Vizserver 3.1 Application Transparent Remote Interactive Visualization and Collaboration

http://subs.emis.de/LNI/Proceedings/Proceedings55/GI-Proceedings.55–20.pdf