Obsah

1. Zobrazení rastrových dat vlastními zobrazovacími prostředky

2. Základní vlastnosti navrhovaného řadiče grafického displeje

3. Implementace řadiče grafického displeje

4. Význam jednotlivých časových úseků

5. Obsah dalšího pokračování tohoto seriálu

1. Zobrazení rastrových dat vlastními zobrazovacími prostředky

Velmi zajímavým a implementačně kupodivu ne až tak složitým způsobem zobrazení obrazových dat (zejména rastrových, tj. bitmap a pixmap) je implementace vlastního grafického subsystému. Tento způsob zobrazení je ze všech dříve popisovaných možností zobrazení snímků na počítačích typu PC nejrychlejší, protože se nemusí provádět žádná mnohdy složitá komunikace ani s hostitelským počítačem, ani s grafickou kartou nainstalovanou v hostitelském počítači. Na přídavné zobrazovací kartě (určené například pro port AGP či sběrnici PCI) je vytvořen výstup na monitor počítače, ať už CRT či LCD, či na televizní monitor (televizní monitor se od běžné televize liší zejména tím, že neobsahuje vysokofrekvenční obvod s anténním vstupem). Nejmarkantnější rozdíl mezi těmito zobrazovacími zařízeními tkví zejména v rozličných metodách míchání barvových a synchronizačních signálů a také v podporovaných rozlišeních.

Mezi hlavní nevýhody tohoto způsobu zobrazování patří nutnost implementace vlastního grafického subsystému či použití nějakého existujícího grafického čipu (grafického řadiče), což poněkud komplikuje obvodový návrh vlastní zobrazovací karty a případně i její programování. Také je nutné vytvořit alespoň základní obslužné rutiny pro výstup grafických informací, mezi něž patří vykreslení jednoho bodu (resp. pixelu v pravidelné rastrové mřížce), úsečky a mnohdy také řetězce znaků.

Mezi významné přednosti patří už dříve zmiňovaná rychlost zobrazení a také nezávislost na monitoru, který je připojen k „běžné“ grafické kartě či grafickému akcelerátoru hostitelského počítače, protože pro výstup je použita samostatná zobrazovací jednotka – jedná se tedy o dvoumonitorový či vícemonitorový systém.

Grafický subsystém lze vytvořit buď na základě vhodného řadiče displeje řešeného zákaznickým obvodem (jedná se například o poměrně známé čipy ADV 478 či Motorola 6845, v dřívějších dobách se však také používaly další čipy), dostatečně výkonným mikroprocesorem či signálovým procesorem, nebo vhodně naprogramovaným programovatelným obvodem typu CPLD či FPGA. Při použití zákaznického obvodu je sice návrh celé zobrazovací karty jednodušší, nepříjemné však je, že se musí přesně dodržet formát dat a časování při čtení obrazových dat z framebufferu. Použití vhodného mikroprocesoru či signálového procesoru DSP (Digital Signal Processor) je mnohem flexibilnější, jedná se však o řešení, které z použitého procesoru využije pouze malou část jeho možností, přičemž výpočetní výkon procesoru je využit pouze z několika procent (vzhledem k nutnosti přesné synchronizace výstupu, kdy není v některých případech možné použít přerušení, které by časování signálů porušilo).

Poslední možnost, tj. využití rekonfigurovatelného (programovatelného) obvodu CPLD, je z hlediska flexibility, přesné synchronizace signálů a efektivity využití plochy (čili počtu logických obvodů) na čipech zdaleka nejvýhodnější. V dalším textu proto stručně popíšu návrh vlastního grafického zobrazovacího subsystému s využitím obvodů z rodiny Xilinx. Tento návrh je založen zejména na práci Chana Elma: General Purpose Display Controller, ve které je však popsána jednodušší verze grafického subsystému s podporou poměrně malého rozlišení 320×240 pixelů s obrazovou frekvencí 50 resp. 60 Hz.

2. Základní vlastnosti navrhovaného řadiče grafického displeje

Navrhovaný řadič grafického displeje (CRTC – Cathode Ray Tube Controller) umožňuje zobrazovat rastrový obraz buď na analogovém monitoru počítače, nebo na televizním monitoru. Místo analogového monitoru je samozřejmě možné použít i LCD monitor, protože tato dvě zobrazovací zařízení používají stejné rozhraní kompatibilní s grafickými kartami typu VGA (neuvažujeme zde digitální rozhraní, které by vyžadovalo další řadič). Zobrazení na běžném televizoru je také možné, ale až po konverzi výstupních signálů buď na kompozitní signál, nebo na anténní VF vstup, jak to ostatně dělaly již domácí osmibitové počítače.

Podle frekvence použitého oscilátoru je možné vytvářet a následně zobrazit rastrový obraz o rozlišení od základních 320×200 pixelů do cca 800×600 pixelů. Při použití televizního monitoru se používá rozlišení 720×576 pixelů, kritický je zde zejména počet obrazových řádků, počet sloupců není, vzhledem k absenci synchronizačních (hodinových) signálů pro jednotlivé pixely, pevně daný, a může se tak pro různé typy televizních obrazovek lišit. Poznámka: mluvíme zde o rozlišení celých televizních snímků, které jsou při zobrazování na televizi rozděleny na dva půlsnímky s polovičním vertikálním rozlišením.

V navrhovaném řadiči jsou podporovány dva formáty pixelů: buď se jedná o pixely zobrazované v 256 stupních šedi, nebo o plnobarevné (truecolor) pixely zobrazované ve formátu RGB. Formát pixelů může být zvolen tak, aby odpovídal internímu formátu pixelů uložených ve framebufferu grafické karty, včetně možné datové výplně mezi jednotlivými pixely. Ve výplni mohou být uloženy další informace o fragmentech ve framebufferu, typicky jejich z-ová hloubka. Pixely (resp. jejich barvy) jsou v průběhu zobrazování čteny přímo z framebufferu, není tedy zapotřebí vytvářet další přídavné fronty (queues) ani jiné typy vyrovnávacích pamětí. Jediným požadavkem je rozdělení framebufferu na přední a zadní barvový buffer, aby se zamezilo současnému přístupu do framebufferu od rastrovací jednotky a od řadiče paměti. Důvodem, proč nebyl použit paletový režim, je zjednodušení návrhu celé grafické karty, protože není zapotřebí implementovat tabulku LUT (do které musí přistupovat jak procesor, tak i grafická karta – viz poruchy v obrazu na kartách VGA).

Rekonfigurovatelný obvod Xilinx může být naprogramován tak, aby četl obrazová data buď z dynamické paměti DRAM, nebo statické paměti SRAM. V případě, že se použije dynamická paměť DRAM, je použito zjednodušeného přístupu do této paměti s výběrem paměťových buněk pomocí signálů RAS (výběr řádku) a CAS (výběr sloupce). Také je možné automaticky generovat prázdné instrukce čtení, pomocí kterých se provádí obnova (refresh) obsahu dynamických pamětí. Pokud se použije konfigurace grafického akcelerátoru s framebufferem uloženým ve statické paměti SRAM, přístup do paměti se značně zjednoduší – používá se jednoduchý výběr dat s posláním jedné adresy a nejsou samozřejmě generovány ani žádné další instrukce čtení pro obnovu obsahu paměti, jelikož tato operace u pamětí typu SRAM postrádá smysl.

Minimální kapacity pamětí pro uložení jednoho snímku v různých formátech pixelů se liší v závislosti na použitém rozlišení. Z jednoduchého výpočtu vyplývá, že pro menší rozlišení, například 320×200 či 256×192 pixelů, je možné použít čipy pamětí o poměrně malé kapacitě, typicky 1 Mb, čímž je možné dosáhnout zmenšení bitové šířky adresové sběrnice se zachováním barevné hloubky zobrazovaného snímku:

320×200×2=128 000 B=1 024 000 b.

3. Implementace řadiče grafického displeje

Největší část funkcionality navrhovaného řadiče grafického displeje je obsažena v programovatelném čipu typu CPLD, v tomto konkrétním případě se jedná o čip XC 95108 (PLCC), který je rozsahem svých funkcí i svou rychlostí pro řízení displeje dostačující, alespoň co se týče práce v rozlišeních používaných u VGA monitorů či běžných televizních monitorů. Je samozřejmě možné použít i programovatelné čipy s vyšším výkonem, například čipy typu Xilinx Spartan či Spartan II, výkon i plocha těchto čipů by však nebyla pro zobrazování plně využita.

Čip XC 95108 obsahuje celkem 108 buněk s klopným obvodem typu D a dvěma programovatelnými vstupy IN a jedním výstupem OUT, které dohromady tvoří jeden CLB (Configurable Logic Block – konfigurovatelný blok logických členů). Dále je možné pomocí tohoto obvodu přímo řídit 69 vstupně/výstupních portů. Tyto porty jsou využity pro řízení čtení obrazových dat z framebufferu přes k tomu vytvořenou sběrnici. Další vstupně/výstupní porty na čipu XC 95108 jsou využity na výstupu (tj. v režimu output) pro sériové posílání barvových informací o jednotlivých pixelech a pro výstup horizontálních a vertikálních synchronizačních signálů V-sync a H-sync.

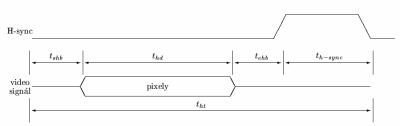

Obrázek 1: Základní časování při generování rastrového snímku řadičem grafického displeje

Jedním z typických rozlišení je takzvané rozlišení VGA, při jehož použití je frekvence hodinových impulsů nastavena na hodnotu 25,175 MHz. Tato frekvence je poněkud vyšší než hodnota spočítaná prostým vynásobením počtu pixelů ve snímku snímkovou frekvencí. Je tomu tak kvůli nutnosti generování horizontálních a vertikálních synchronizačních impulsů a také pro vytváření tmavých okrajů na obrazovce, ve kterých není žádný obraz vytvářen. Tmavé okraje (nazývané border, overscan, blank lines/columns) jsou vytvořeny na každém obrazovém řádku po pravém i levém okraji obrazovky. Je také vytvořeno několik zcela tmavých obrazových řádků na horním a/nebo spodním okraji obrazovky. Základní časování a průběh signálů při generování snímku jsou patrné z následujících obrázků.

4. Význam jednotlivých časových úseků

Význam jednotlivých časových úseků na obrázcích je následující:

| Označení | Plný název | Význam |

|---|---|---|

| tht | Horizontal Total Time | čas nutný pro zobrazení celého obrazového řádku i se zatemněnými okraji |

| thd | Horizontal Display Time | čas, po který se zobrazují viditelné pixely na řádku |

| tshb | Start Horizontal Blank | časový úsek po který je generován zatemněný levý okraj |

| tehb | End Horizontal Blank | časový úsek pro generování pravého okraje |

| th-sync | Horizontal Sync Time | časový úsek nutný pro návrat elektronového paprsku na začátek následujícího obrazového řádku |

| tvt | Vertical Total Time | čas nutný pro zobrazení celého snímku i s horním a dolním zatemněným okrajem |

| tvd | Vertical Display Time | čas, po který se zobrazují viditelné obrazové řádky |

| tsvb | Start Vertical Blank | časový úsek pro generování horního okraje obrázku |

| tevb | End Vertical Blank | časový úsek pro generování dolního okraje obrázku |

| tv-sync | Vertical Sync Time | časový úsek nutný pro návrat elektronového paprsku na začátek (levý horní okraj) nového snímku |

Řadič grafického displeje, který je u navrhovaného grafického akcelerátoru reprezentovaný obvodem XC 95108, však není naprogramován pro úlohu, ve které by přesně měřil či sledoval nějaké časové úseky. Místo toho je vhodně zvolena základní frekvence oscilátoru s vestavěným krystalem tak, aby se veškeré delší časové úseky daly z této frekvence jednoduše odvodit, tj. aby všechny časy byly celočíselnými násobky jedné periody oscilátoru.

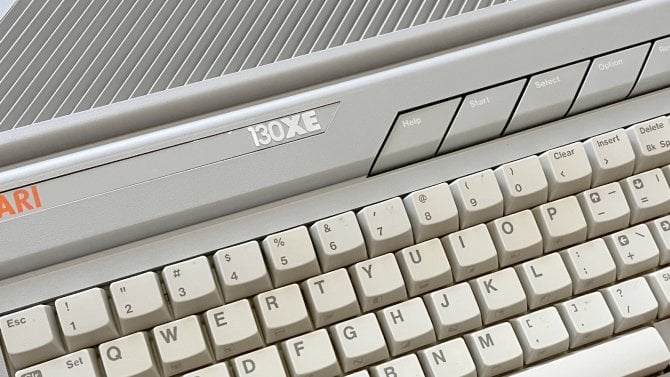

V navrhovaném řadiči je zvolena přesně taková frekvence oscilátoru, aby se při jednom hodinovém taktu tc vygenerovaly barvové signály a případně i synchronizační signály přesně pro jeden pixel. Tento způsob práce s pixely je sice zřejmý na první pohled, ne všechny řadiče displejů jej však používají. Typické bývají konfigurace, kdy se jeden pixel přenese za polovinu hodinového taktu, což mimo jiné znamená, že synchronizace neprobíhá na úrovni pixelů, ale jejich dvojic (toto řešení bylo použito i u osmibitových počítačů Atari v grafickém módu 8 – v tomto režimu nebylo kvůli tomu možné používat dvě barvy).

Veškeré výše zmíněné časy jsou při tomto nastavení dodrženy pomocí binárních čítačů vytvořených z CLB obvodů na čipu XC 95108. Čítače jsou nastaveny na hodnotu, která odpovídá poměru měřeného času k periodě oscilátoru a čítají směrem k nule (od nastavené hodnoty se po uplynutí jednoho hodinového taktu tc odečte jednotka. Po dosažení nuly je interně, tj. přímo na obvodu, vygenerován signál, který indikuje dosažení měřeného časového okamžiku – viz druhý ilustrační obrázek.

Obrázek 2: Průběh signálů generovaných řadičem grafického displeje při přenosu jednoho obrazového řádku

Obrázek 3: Průběh signálů generovaných řadičem grafického displeje při přenosu celého snímku

Obrázek 4: Způsob měření všech časových průběhů z jednoho zdroje hodinových impulsů tc

5. Obsah dalšího pokračování tohoto seriálu

V dalším pokračování tohoto seriálu dokončíme popis vlastní grafické karty. Budeme se věnovat především způsobům zobrazení rastrových snímků na televizním monitoru i analogovém VGA monitoru.