Obsah

1. Historie vývoje počítačových her (106. část – herní konzole Sega Saturn)

2. Architektura herní konzole Sega Saturn

3. RISCové mikroprocesory Hitachi SH-2

4. Instrukční pipeline, branch delay sloty a instrukční soubor mikroprocesorů SH-2

5. Čip SMPC (System Manager and Peripheral Control)

6. Čip SCU (System Control Unit)

8. Základní informace o grafickém subsystému herní konzole Sega Saturn

9. Struktura obrazové paměti herní konzole Sega Saturn

10. Obsah následující části seriálu

1. Historie vývoje počítačových her (106. část – herní konzole Sega Saturn)

V dnešní části seriálu o historii vývoje her i herního hardware se seznámíme s technickými parametry i interní strukturou další herní konzole páté generace – Sega Saturn. Minule jsme si popsali herní konzoli Atari Jaguar, jejímž význačným rysem bylo využití několika čipů, které musely vzájemně spolupracovat, a to jak při výpočtech, tak i (a to především) při vykreslování herního světa. Navíc byl mikroprocesor Atari Jaguaru postaven na architektuře RISC, což byla poměrně velká změna oproti starším konzolím čtvrté generace, která v důsledku vedla k rychlejšímu přechodu vývojářů na vyšší programovací jazyky ©, jenž se pro větší část kódu stal náhradou assembleru. Dnes popisovaná konzole Sega Saturn je postavena na podobné filozofii většího množství spolupracujících čipů (což ovšem způsobilo problémy hlavně zmíněným vývojářům), ovšem v mnoha ohledech se tyto konzole od sebe odlišují; především se to týká grafických subsystémů obou zmiňovaných herních konzolí.

V herní konzoli Sega Saturn nalezneme větší množství čipů, jejichž jména a základní funkce jsou vypsány v následující tabulce:

| # | Čip | Plné jméno | Funkce |

|---|---|---|---|

| 1 | SH-2 | Hitachi SuperH-2 | dvojice RISCových mikroprocesorů |

| 2 | SCU | System Control Unit | řízení sběrnic a koordinace ostatních čipů, centrální jednotka konzole |

| 3 | SMPC | System Manager and Peripheral Control | řízení RESETu, přepínání horizontálního rozlišení, čtení stavu ovladačů |

| 4 | SCSP | Saturn Custom Sound Processor | zvukový čip (Yamaha YMF292) |

| 5 | VDP1 | Video Display Processor 1 | první část grafického subsystému |

| 6 | VDP2 | Video Display Processor 2 | druhá část grafického subsystému |

| 7 | MC68E000 | Motorola MC68E000 | řízení zvukového čipu SCSP |

| 8 | DSP | DSP MC68E000 | řízen CPU, může provádět různé funkce (nejde o samostatný čip, ale o modul) |

2. Architektura herní konzole Sega Saturn

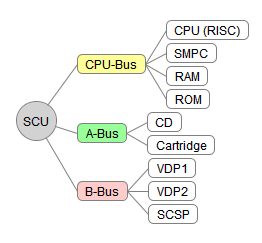

V této kapitole si stručně popíšeme základní architekturu herní konzole Sega Saturn. Vzhledem k tomu, že tato konzole obsahuje velké množství různých čipů, které si musí navzájem vyměňovat data a navíc musí načítat i ukládat data do operační paměti či do paměti obrazové, stáli konstruktéři Saturnu před problémem, jakým způsobem budou jednotlivé moduly navzájem spolupracovat. Výsledkem snahy o zajištění vzájemné komunikace na jedné straně a autonomní práce jednotlivých čipů na straně druhé je schéma, které můžete vidět na obrázku číslo 1. Z tohoto schématu je patrné, že ústředním řídicím prvkem je zde čip SCU (System Control Unit), jehož hlavním úkolem je řídit přístup ke třem sběrnicím, kterými je herní konzole Sega Saturn vybavena. Kromě samotného řízení je umožněn i blokový přenos dat s použitím DMA (Direct Memory Access), čehož je možné využít například při zápisu rastrových obrázků z hlavní paměti do framebufferu, „krmení“ zvukového subsystému daty apod.

Obrázek 1: Blokové schéma herní konzole Sega Saturn.

První sběrnice Saturnu nese všeříkající název CPU-Bus, a to z toho důvodu, že jsou na ni připojeny jak oba hlavní mikroprocesory popsané v navazující kapitole, tak i operační paměť o kapacitě 2 MB i paměť ROM o kapacitě 512 kB. Dále zde nalezneme čip SMPC, jenž mj. slouží pro čtení stavů ovladačů. Další sběrnice se jmenuje A-Bus. K této sběrnici je připojeno rozhraní pro CD mechaniku a navíc tato sběrnice zajišťuje čtení popř. zápis na paměťové cartridge. Třetí sběrnice pojmenovaná B-Bus slouží pro přenos dat k oběma video procesorům (tedy ke grafickému subsystému) i k čipu SCSP, tj. k subsystému zvukovému. Důvodem pro oddělení jednotlivých čipů a jejich umístění na různé sběrnice byla snaha o zajištění relativní nezávislosti práce jednotlivých modulů, ovšem za cenu komplikovanějšího vývoje (s tímto problémem se v menší míře setkáváme i dnes, kdy například není vhodné měnit hodnoty jednotlivých pixelů či texelů v rastrových obrázcích či texturách, které již jsou přeneseny na paměť grafického akcelerátoru).

3. RISCové mikroprocesory Hitachi SH-2

Z pohledu vývojáře her jsou nejdůležitějšími čipy nainstalovanými v herní konzoli Sega Saturn samozřejmě mikroprocesory. Množné číslo zde používám schválně, protože Saturn byl ve skutečnosti obsazen dvojicí spolupracujících třicetidvoubitových mikroprocesorů, což mělo – alespoň podle původních plánů – vést ke zvýšení čistého výpočetního výkonu této herní konzole prakticky na dvojnásobnou hodnotu. Ve skutečnosti se však dosahovalo přibližně 1,5 násobku výkonu jediného čipu, a to z toho důvodu, že oba čipy sdílely společnou sběrnici, což se negativně projevovalo při přístupu do operační paměti. Saturn byl obsazen mikroprocesory SH-2 (plným jménem SuperH) vyráběnými společností Hitachi. Jedná se o procesory s architekturou RISC, které byly a dodnes jsou používány v mnoha oblastech. Z historického pohledu je pro nás zajímavé jejich použití v konzolích Sega 32X a právě Sega Saturn, ovšem tyto čipy se používají i v různých multimediálních zařízeních, automotive průmyslu (řídicí jednotky motorů), digitálních kamerách, MPEG přehrávačích atd.

Každý z mikroprocesorů obsahoval vyrovnávací paměť o kapacitě 4kB, která alespoň do určité míry zlepšovala reálný výpočetní výkon (eliminovaly se některé kolize při přístupu do operační paměti). Oba čipy SH-2 sice vycházely z „klasického“ modelu RISCových procesorů, ovšem v jejich interní struktuře najdeme prvky inspirované DSP i mikrořadiči (což ostatně vychází i z výše uvedeného způsobu využití těchto čipů v praxi). Každý mikroprocesor obsahovat šestnáct pracovních registrů, z nichž každý měl šířku 32bitů. Registr s indexem 0 (R0) mohl být využit jako indexový registr, zatímco registr s indexem 15 (R15) se používal ve funkci ukazatele na vrchol zásobníku (SP). Kromě pracovních registrů mohl programátor využívat i 32bitové řídicí registry (Global Base Register a Vector Base Register) i takzvané systémové registry. Ty byly využívány pro ukládání výsledků operace typu MAC (multiply and accumulate), kterou můžeme najít v mnoha digitálních signálových procesorech (DSP).

4. Instrukční pipeline, branch delay sloty a instrukční soubor mikroprocesorů SH-2

Mikroprocesory SH-2 obsahovaly instrukční pipeline s pěti řezy, což znamenalo, že v každém cyklu bylo možné v ideálním případě dokončit jednu instrukci. Výjimkou je výše zmíněná operace MAC, která v případě násobení dvou šestnáctibitových hodnot (s 32bitovým výsledkem) trvala dva cykly a v případě násobení dvou 32bitových hodnot (s 64bitovým výsledkem) dokonce čtyři cykly. Zajímavé a pro RISCové procesory poněkud neobvyklé taktéž je, že mnoho instrukcí mohlo provádět post inkrement popř. pre dekrement pracovního registru použitého pro adresování. V závislosti na velikosti operandu se hodnota (adresa) uložená v registru zvýšila či snížila o 1 (byte), 2 (short) či 4 (int), takže se tyto operace prováděné vlastně zadarmo (současně s hlavní operací) mohly použít například při práci s poli. Mimochodem – tyto operace byly oblíbené již na mikroprocesorech Motorola řady 6809 a 68×00, protože poměrně přesně kopírovaly některé obraty používané ve vyšších programovacích jazycích.

Pro některé DSP a především pak RISCové procesory (jmenujme například MIPS, PA-RISC či SPARC) je poměrně obvyklá taktéž technologie takzvaných branch delay slotů, kterou najdeme i u zde popisovaných čipů SH-2. SH-2 měl jeden delay slot, což znamenalo, že instrukce uložená ihned za instrukcí podmíněného či nepodmíněného skoku byla vykonána vždy, bez ohledu na výsledek skoku (zda se provede či neprovede). Díky existenci této technologie se mohla lépe využít instrukční pipeline, neboť pipeline nebylo nutno celou vyprazdňovat po každém skoku (což znamenalo zdržení až čtyři takty). Mimochodem – podmíněné skoky byly prováděny na základě stavového bitu T, který zde zastupoval jak pravdivostní hodnotu true/false, tak i příznak Carry (bitové posuny a rotace, sčítání a odčítání s přenosem). Všechny instrukce čipu SH-2 měly šířku jen šestnáct bitů (u běžných RISC procesorů je šířka dvojnásobná), což bylo u herní konzole Sega Saturn velmi výhodné kvůli již zmíněné relativně malé kapacitě paměti cache a nutnosti synchronizace obou mikroprocesorů při přístupu do hlavní paměti.

5. Čip SMPC (System Manager and Peripheral Control)

Dalším čipem, který můžeme v herní konzoli Sega Saturn najít, je integrovaný obvod nazvaný SMPC, neboli celým jménem System Manager and Peripheral Control. V porovnání s ostatními moduly popsanými v tomto článku se jedná o relativně jednoduchý čip, který je interně řízený čtyřbitovým procesorem (samotný program pro tento mikroprocesor je uložen jako firmware a nelze ho tedy změnit). Čip SMPC má kromě zmíněného interního mikroprocesoru tři další moduly. Prvním z nich jsou hodiny reálného času. Další modul se jmenuje SM (System Manager). Úkolem tohoto modulu je řízení signálu RESET takovým způsobem, aby byly správně inicializovány všechny ostatní čipy Saturnu. Kromě toho se tento modul stará i o přepínání horizontálního rozlišení mezi 320 a 352 body na jeden obrazový řádek (to částečně souvisí se změnou časování ostatních čipů). Na vstupu tohoto modulu se nachází dvojice sedmibitových paralelních portů (jde o jednoduchou paralelní bránu podobnou klasickému čipu 8255) použitá pro připojení, čtení a řízení periferních zařízení.

Třetí důležitý modul implementovaný na čipu SMPC se jmenuje PC neboli Peripheral Control. Tento modul je určen především pro čtení aktuálního stavu herních ovladačů a pro řízení samostatné CD mechaniky. Na chvíli se nyní zastavme u herních ovladačů, protože se (celkem logicky) pro mnoho hráčů jedná o velmi důležitou část herní konzole. Pro Segu Saturn byly navrženy ovladače s D-padem a devíti tlačítky (A, B, C, X, Y, Z, tlačítko na levém a pravém horním okraji a tlačítko Start), nicméně použít bylo možné i starší třítlačítkové a šestitlačítkové ovladače z konzole Sega Mega Drive/Sega Genesis – tyto ovladače byly systémem podporovány, takže bylo nutné jen použít konvertor. Navíc bylo čipem SMPC podporováno i připojení myši a později se pro objevil i 3D Control Pad s analogovými ovládacími prvky.

6. Čip SCU (System Control Unit)

O čipu SCU (System Control Unit) jsme si již základní informace řekli v předchozích kapitolách. Jedná se o ústřední řídicí modul celé herní konzole Sega Saturn, protože právě SCU dokáže řídit přístup ke třem nezávislým sběrnicím CPU-Bus, A-Bus i B-Bus. SCU navíc obsahuje i řadič pro DMA, přičemž DMA může běžet nezávisle na CPU-Bus, což znamená, že oba mikroprocesory mohou relativně nezávisle provádět výpočty, zatímco se budou přenášet například data do grafického subsystému. DMA kanály lze nakonfigurovat různým způsobem, například pro přenos mezi operační pamětí a zařízením na A-Bus, zařízením na B-Bus a pamětí, přenášet data mezi A-Bus a B-Bus atd. Na SCU je implementován i řadič přerušení, na němž je zajímavé, že je podporováno 32 zdrojů přerušení, z toho 14 přerušení interních (dva časovače, horizontální i vertikální zatemnění, DSP, přerušení od jednoho ze tří DMA kanálů, zvukového systému atd.) a šestnáct zdrojů externích (dva zdroje z možných třiceti dvou zůstaly nevyužity).

Kromě toho obsahuje čip SCU i dvojici časovačů, z nichž první je desetibitový a je řízen signálem V-Blank (vertikální zatemnění, proběhne každý snímek) a jeho stav je snižován po každém H-Blank (horizontální zatemnění, každý obrazový řádek). Díky způsobu řízení tohoto časovače ho lze využít například pro zahájení provádění nějakého grafického efektu na určitém obrazovém řádku. Druhý časovač je jen devítibitový, nastavován je při každém H-Blank (tj. na každém obrazovém řádku) a jeho hodnota je snižována po vykreslení jednoho pixelu (1/4 frekvence systémových hodin). Z toho vyplývá, že díky existenci tohoto časovače je možné nějakou akci nastavit přesně na konkrétní místo na obrazovce, čehož se opět využívalo pro provádění různých grafických efektů (nebylo zapotřebí přesně počítat, kolik pixelů se již vykreslilo atd.). Oba časovače mohly při dočítání do nuly generovat přerušení zpracované opět modulem SCU.

7. DSP umístěný na čipu SCU

Součástí čipu SCO popsaného v předchozí kapitole je i digitální signálový procesor, který nevykonává žádné předem zadané funkce, ale bylo možné mu zadat prakticky jakoukoli výpočetní úlohu (zpracování obrazu, zpracování zvuku). Zajímavé je, že o přenos vlastního programového kódu (sekvence strojových instrukcí) a následovné spuštění programu na DSP se musel postarat jeden z hlavních procesorů (SH-2), takže z tohoto pohledu je možné DSP považovat spíše za podpůrný obvod, i když jeho možnosti nebyly nikterak malé a ani výpočetní výkon nebyl v žádném případě nezanedbatelný – spíše naopak. DSP byl vybaven pamětí RAM pro uložení programu o kapacitě 256×32 bitů. Kapacita paměti pro data byla taktéž rovna 256×32 bitům. Připojen byl k externí 32bitové sběrnici a dokázal pracovat s hodinovou frekvencí 28 MHz (podobně jako zbylé části systému). Aritmeticko-logická jednotka byla taktéž 32bitová a dokázala zpracovat běžné instrukce typu součet, rozdíl, bitové operace a bitové posuny a rotace (AND, OR, XOR, ADD, SUB, AD2, SR, RR, SL, RL, RL8, CLR).

Násobička nebyla součástí ALU, ale pracovala samostatně (navíc asynchronně, což pro tento typ modulu dává smysl); dokonce pro ni byly vyhrazeny speciální registry, do nichž se nejprve uložily oba operandy a následně se násobička spustila. Vynásobit bylo možné dva operandy s šířkou 32 bitů, přičemž výsledkem byla 48 bitová hodnota uložená opět do speciálního registru. DSP dále obsahoval klasické instrukce pro podmíněné skoky a navíc i instrukce, které mohly zahájit přenos dat po sběrnici, včetně spuštění DMA. Zajímavý byl formát instrukcí – každé instrukční slovo mělo šířku třicet dva bitů a v některých případech bylo možné do jednoho slova uložit větší množství instrukcí: ALU operace, přenos dat po sběrnici atd., takže v tomto DSP nalezneme určité prvky architektury VLIW (Very Long Instruction Word).

Upozornění: termín DSP se v konzoli Sega Saturn používá pro popis několika modulů, ať již se jedná o zde popsané DSP, tak i o DSP, jenž je součástí SH-2 či zvukového subsystému.

8. Základní informace o grafickém subsystému herní konzole Sega Saturn

Velmi neobvyklým způsobem byl vyřešen grafický subsystém herní konzole Sega Saturn. O vykreslování obrazu se starala dvojice takzvaných video procesorů pojmenovaných VDP 1 a VDP 2. Tyto samostatně pracující čipy byly umístěny na sběrnici B-Bus a obrazová data měly uloženy ve framebufferu odděleném od hlavní operační paměti. Jedná se tedy o podobné řešení, s jakým se můžeme setkat i u moderních grafických akcelerátorů. Herní konzoli Sega Saturn bylo možné připojit k televizoru pracujícím v normě PAL nebo NTSC (v závislosti na regionu, kde byla konzole prodávána) a dostupné byly základní grafické režimy s rozlišením 320×224 pixelů, 320×240 pixelů, 352×224 pixelů a 352×240 pixelů, a to při použití barevné hloubky 8 či 16bpp. Horizontální i vertikální rozlišení bylo možné dvojnásobně zvýšit (prokládané režimy se všemi svými nevýhodami), ovšem za cenu snížení barevné hloubky jen na 8bpp.

9. Struktura obrazové paměti herní konzole Sega Saturn

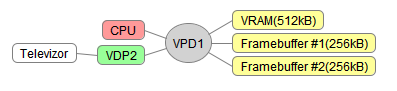

I struktura obrazové paměti je poměrně neobvyklá. Tato paměť totiž byla rozdělena na několik regionů. Konkrétně to znamená, že video procesor VDP 1 měl přístup k jednomu megabajtu DRAM, přičemž 512kB z této kapacity bylo použito pro uložení „vykreslovacích příkazů“ (příkazy zahrnovaly sprity, úsečky, polyčáry, polygony složené ze čtyřúhelníků, nastavení souřadného systému atd.) a samotný framebuffer byl rozdělen na dvě části, z nichž každá měla kapacitu 256kB. Není těžké vypočítat, že kapacita této paměti skutečně dostačovala pro uložení celého snímku (352×240 pixelů v 16bpp atd.). Druhý video procesor VDP 2 měl přístup k dalším 512 kB RAM. Podrobnějšímu popisu funkcí obou video procesorů se budeme věnovat v navazující části tohoto seriálu.

Obrázek 2: Grafický subsystém herní konzole Sega Saturn.

10. Obsah následující části seriálu

V následující části tohoto seriálu se budeme zabývat popisem zbývajících modulů a čipů, které byly nedílnou součástí herní konzole Sega Saturn. Jedná se především o oba video procesory pojmenované VDP1 a VDP2. Vlastnosti těchto čipů byly navrženy takovým způsobem, aby byly dobře využitelné jak pro 2D hry (scrolling, podpora spritů atd.), tak i pro 3D hry (možnost zobrazit otexturovaný čtyřúhelník). Jednalo se však o hardware, který byl značně odlišný od „klasických“ 3D akcelerátorů, což mj. znamenalo pro výrobce her nemalé problémy při používání 3D modelů získaných na jiných systémech atd. Kromě vlastností obou video procesorů si taktéž popíšeme zvukový subsystém Saturnu, jenž byl taktéž poměrně neobvyklý a přitom velmi flexibilní, protože kombinoval možnosti DSP se zvukovou syntézou (FM syntéza ostatně byla použita i ve starších herních konzolích společnosti Sega).

11. Odkazy na Internetu

- Sega documentation

http://koti.kapsi.fi/~antime/sega/docs.html - 1995 Programming on the Sega Saturn

http://cowboyprogramming.com/2010/06/03/1995-programming-on-the-sega-saturn/ - Sega Myths-Saturn was the most difficult console to program for of 5th Gen

http://forums.sega.com/showthread.php?313485-Sega-Myths-Saturn-was-the-most-difficult-console-to-program-for-of-5th-Gen - SuperH RISC engine Family

http://www.renesas.com/products/mpumcu/superh/index.jsp - Sega Saturn

http://en.wikipedia.org/wiki/Sega_saturn - Jaguar Sector – II

http://www.jaguarsector.com/index.php - Atari Age: Atari Jaguar History

http://www.atariage.com/Jaguar/history.html - Jaguar

http://www.giantbomb.com/jaguar/3045–28/ - Consoles that won't die: The Atari Jaguar

http://venturebeat.com/2013/04/25/consoles-that-wont-die-atari-jaguar/ - Atari Jaguar and Atari Jaguar CD

http://videogamecritic.com/jaguarinfo.htm - Atari Jaguar Documentation (Forum)

http://www.jaguarsector.com/index.php?showforum=65 - Atari Jaguar Programming (Forum)

http://www.jaguarsector.com/index.php?showforum=63 - The Jaguar Underground Documentation

http://justclaws.atari.org/devcats/dox/dox.htm - Blitter (Wikipedia CZ)

http://cs.wikipedia.org/wiki/Blitter - Blitter (Wikipedia EN)

http://en.wikipedia.org/wiki/Blitter - Bit blit

http://en.wikipedia.org/wiki/Bit_blit - Disassembler for the portable Jaguar DSP emulator (zdrojový kód s instrukcemi)

http://mamedev.org/source/src/emu/cpu/jaguar/jagdasm.c.html - Fourth-Generation Consoles

http://gaming.wikia.com/wiki/Fourth-Generation_Consoles - Fifth-Generation Consoles

http://gaming.wikia.com/wiki/Fifth-Generation_Consoles - History of video game consoles (fifth generation)

http://en.wikipedia.org/wiki/History_of_video_game_consoles_(fifth_generation) - Atari Jaguar

http://gaming.wikia.com/wiki/Atari_Jaguar - Atari Jaguar Games

http://gaming.wikia.com/wiki/List_of_Atari_Jaguar_games - MyMedia Games Network Retrospective – Nintendo Super FX chip

http://psp.mmgn.com/News/MyMedia-Games-Network-Retrospe-G6W - Wikipedia: Super FX

http://en.wikipedia.org/wiki/Super_FX - IGN: Top 25 Consoles

http://www.ign.com/top-25-consoles/13.html - Sega Mega Drive

http://sega.jp/archive/segahard/md/ - The16bit Era Of Console Video Games

http://tvtropes.org/pmwiki/pmwiki.php/Main/The16bitEraOfConsoleVideoGames - The Console Wars

http://www.cracked.com/funny-2590-the-console-wars/ - Console Wars

http://tvtropes.org/pmwiki/pmwiki.php/Main/ConsoleWars - Era of the „Bit Wars“

http://www.gtplanet.net/forum/threads/era-of-the-bit-wars.119796/ - Rez Wars: How the Bit Wars never really ended

http://www.ign.com/blogs/beastmastertoad/2013/01/31/rez-wars-how-the-bit-wars-never-really-ended - Which system ended the „Bit Wars“?

http://atariage.com/forums/topic/199163-which-system-ended-the-bit-wars/