Obsah

1. Interní sběrnice PCI Express

2. Základy technologie PCI Express

3. Komunikace po PCI Express

4. Oblasti použití PCI Express

5. Interní sběrnice: shrnutí

6. Budoucí vývoj interních sběrnic

7. Přenosové rychlosti nejpoužívanějších sběrnic v PC

8. Literatura a odkazy na Internetu

9. Obsah následující části seriálu

1. Interní sběrnice PCI Express

V předchozích čtyřech částech tohoto seriálu bylo popsáno mnoho typů interních sběrnic, které měly i přes mnoho výkonnostních i architektonických rozdílů jednu společnou vlastnost: adresy, data i příkazy (a stavy) se přenášely paralelně po několika vodičích. Původní osmibitová sběrnice ISA měla osm vodičů určených pro synchronní přenos dat, šestnáctibitová sběrnice ISA šestnáct vodičů, „pětivoltová“ PCI 32 vodičů, 64bitová PCI 64 vodičů atd. Paralelní přenos dat se při menších hodinových frekvencích sběrnic jevil jako výhodný, jelikož umožňuje přenést větší množství bitů současně (ideálně celé slovo zpracovávané mikroprocesorem), není nutné vytvářet relativně složité obvody pro serializaci a deserializaci dat (na koncích sběrnice postačují jednoduché záchytné registry – latche) apod. Ovšem ve chvíli, kdy se zvyšuje hodinová frekvence sběrnic, se již začínají projevovat některé nežádoucí jevy, které frekvenci (a tím i maximální přenosovou rychlost) omezují – rozdílné zpoždění na jednotlivých datových vodičích, vzájemné rušení, zkreslení signálů atd.

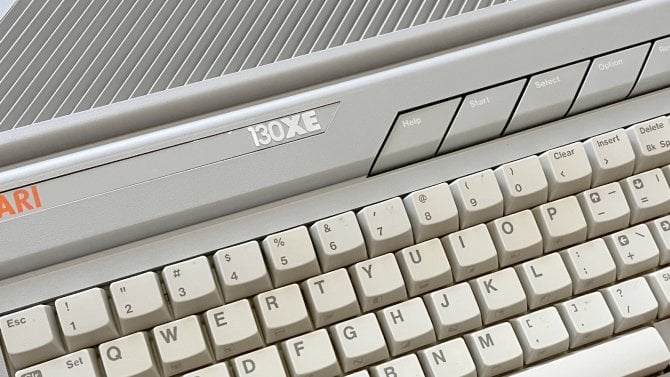

Obrázek 1: Grafická karta určená do sběrnice PCI Express ×16

Nejvýrazněji se však nevýhoda paralelního přenosu projeví ve chvíli, kdy se přechází z klasické sběrnicové topologie (ve které jsou všechny karty připojeny na stejné linky o něž se musí dělit na základě pokynů arbitrážního obvodu) na topologii odlišnou, ve které se počet spojů (ať již realizovaných fyzicky přímo na základní desce, či logicky v přepínači – switchi) mezi připojenými kartami zvyšuje. Všechny zmíněné problémy je možné vyřešit překvapivě snadno, konkrétně přechodem na sériový způsob přenosu dat. To sice vede k nutnosti použití složitějších obvodů ve vlastních zařízeních (přechod na sériový způsob přenosu vede k zavedení paketové technologie), na stranu druhou se však paradoxně snižují náklady na výrobu základní desky i karet. Navíc je možné do jedné karty vést více relativně samostatně pracujících sériových linek a tím zvýšit maximální přenosové rychlosti. Právě touto cestou, která je mj. použita i v klasickém Ethernetu, se vydali tvůrci relativně nové sběrnice PCI Express.

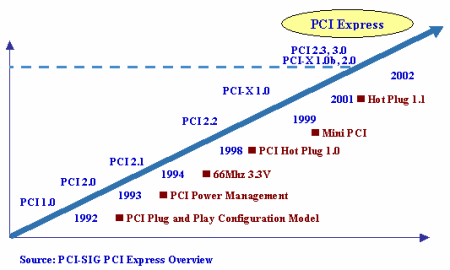

Obrázek 2: Sběrnice PCI Express má s původní sběrnicí společné jméno a logickou vrstvu. Na úrovni fyzické se jedná o naprosto odlišné technologie. Vývoj standardu zastřešuje stejná organizace, proto bylo zvoleno i podobně znějící jméno…

2. Základy technologie PCI Express

PCI Express používá pro přenos adres, dat i prakticky všech řídicích signálů dva páry vodičů; každý pár vodičů přitom provádí přenos v jednom směru s rychlostí 2,525 Gigabitů za sekundu (u verze 2 je to dvojnásobek). Všechny čtyři vodiče tvořící ony dva páry se nazývají lane (pruh, dráha). Důvod, proč se v každém směru používá dvojice vodičů a nikoli vodič jeden (jehož potenciál by se porovnával s jedinou „zemí“), spočívá v tom, že dva vodiče mohou tvořit uzavřenou proudovou smyčku, po které je možné data přenášet velmi vysokou rychlostí, aniž by docházelo k většímu vyzařování signálu do okolí (naproti tomu u klasických paralelních sběrnic fungují jednotlivé vodiče jako antény). Karty, které pro svoji funkci nevyžadují velké datové toky, mohou použít pouze jednu dráhu, čímž je efektivně dosaženo přenosové rychlosti cca 250 MB.s-1 v obou směrech (reálná přenosová rychlost bude o cca 5 procent nižší, protože je nutné přenášet i řídicí sekvence, opravné kódy atd). Jak se z hodnoty cca 2,5 Gb.s-1 získala hodnota 250 MB.s-1, když byte obsahuje osm bitů? Při přenosu je použito kódování 8b/10b, tj. každých osm bitů surových dat je převedeno na deset bitů, přičemž je zajištěna maximální délka sekvence nul a jedniček – to je nutné pro synchronizaci přenosu na tak vysokých rychlostech, i když se tím přenosové pásmo sníží o 25%.

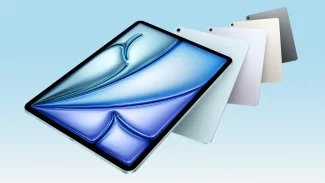

Obrázek 3: Karta určená do sběrnice PCI Express ×1, kterou je však možné zapojit i do všech širších konektorů PCI Express – ×2, ×4, ×8 i ×16

U karet, které vyžadují větší datové toky (například se jedná o grafické akcelerátory), je možné použít několika drah současně zavedených do jednoho konektoru. Délka konektoru a počet jeho pinů se samozřejmě zvětšuje. Podle počtu drah se takové konektory a karty označují ×1 (jedna dráha), ×2 (dvě dráhy), ×4, ×8, ×12, ×16 až ×32. V běžných počítačích se setkáme především s konektory typu ×1 a ×16, někdy však konektory ×16 ve skutečnosti pracují v režimu ×8, což je případ některých základních desek, které obsahují dva „×16“ konektory určené pro grafické karty. Zajímavé a užitečné je, že i v konektoru ×16 je možné použít kartu, která má menší počet drah (×1, ×2 atd.). Taková karta bude pracovat, i když samozřejmě na nižší rychlosti. Některé základní desky dokonce obsahují kratší konektory s jedním otevřeným koncem, do kterých je možné zasunout i karty delší, čímž se teoreticky dá karta například s šestnácti drahami umístit do konektoru ×1. O počtu použitých drah se rozhoduje při inicializaci PCI Express.

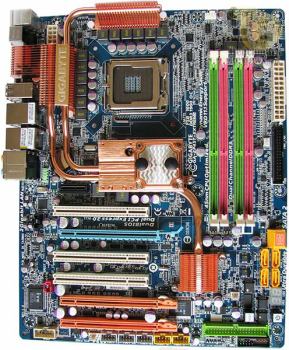

Obrázek 4: Základní deska obsahující čtyři konektory sběrnice PCI Express: ×16 (modrý), ×8 (dlouhý oranžový), a dvojici ×4 (krátké oranžové).

3. Komunikace po PCI Express

Možná nejzajímavější je na sběrnici PCI Express způsob komunikace jednotlivých karet a mikroprocesoru. Jak jsem se již zmínil v předchozích odstavcích, není u PCI Express použita klasická sběrnicová topologie, u které jednotlivé karty musí žádat o přístup na sběrnici a sdílet přenosové pásmo s ostatními zařízeními. Místo toho vedou od všech konektorů jednotlivé dráhy do přepínače (switch), který (teoreticky) dokáže libovolné dvě dráhy propojit a vytvořit tak strukturu typu point-to-point. Na jednu stranu je sice nutné, aby byl na základní desce přítomen poměrně složitý přepínač, na stranu druhou však odpadá arbitrážní obvod (který také nebyl zcela jednoduchý) a především: každá dráha může přenášet data maximální rychlostí (samozřejmě obousměrně, čehož se však nedá vždy zcela využít) a zařízení se tak nemusí dělit o jedno přenosové pásmo tak, jak tomu bylo například u sběrnice PCI. Proč se však stále mluví o „sběrnici“, když je použita jiná topologie? Na úrovni řízení se totiž ovládacím programům zařízení skutečně jeví tak, jako by byla připojena na sběrnici, i když se na úrovni vlastních vodičů o sběrnici nejedná. Podobně je tomu ostatně i u externí „sběrnice“ USB.

Obrázek 5: Vlevo: dvě grafické karty pracující v režimu ×16. Vpravo: čtyři grafické karty pracující v režimu ×8

Díky tomuto uspořádání je možné mít v serveru nainstalováno větší množství gigabitových Ethernetových adaptérů (každému postačuje konektor ×1) či ve výkonné stanici několik grafických karet (×8, ×16) – to nebylo s technologií AGP vůbec možné. Extrémní případ je ukázán na dalším obrázku – čtyři grafické karty, každá připojená do konektoru ×16 (reálně však používajícím osm drah). Při přenosu dat je použita paketová technologie známá například ze systému Ethernet, tj. vlastní užitečná data se přenáší spolu s řídicími kódy, kódy pro detekci chyb atd. To poněkud snižuje reálnou maximální dosažitelnou rychlost. Uvádí se, že cca 5 % přenosové kapacity je použito právě pro přenos dodatečných informací, přičemž se toto číslo zvětšuje v případě, že jsou přenášené bloky malé. U zařízení, která mají nejvyšší nároky na přenosovou rychlost, zejména u grafických karet, se však většinou provádí přenos větších bloků dat, který je na PCI Express řešený efektivně.

Obrázek 6: Základní deska s jedním konektorem PCI Express ×16 (modrý), dvěma konektory ×8 (oranžové) a jedním konektorem ×4 (černý). Kromě toho se na desce nachází i tři klasické konektory PCI sběrnice (bílé).

4. Oblasti použití PCI Express

Kromě postupného vytlačování klasické sběrnice PCI nahradila PCI Express i minule popsaný akcelerovaný port AGP. Přitom se v prakticky všech směrech jedná o zásadní vylepšení – PCI Express dovoluje použití vyšších rychlostí než je možné dosáhnout u AGP a také je možné použít větší množství grafických akcelerátorů. Například firma nVidia vytvořila technologii nazvanou dual-SLI založenou na dvojici karet určených do konektoru ×16, přičemž je (ovšem prozatím pouze při použití čipsetu nForce 4) šestnáct drah rozděleno na dvě skupiny po osmi drahách, pomocí kterých mohou být do systému zapojeny dvě shodné grafické karty pracující v tandemu (tyto karty se navíc navzájem propojují zvláštním „můstkem“). Nárůst rychlosti renderingu je skoro dvojnásobný, protože každá karta počítá pouze polovinu obrazu. Podobnou technologii nabízí i konkurenční ATI, ovšem prozatím nejdále jsou grafické karty systému Alienware Video Array, který dokázal vyřešit problémy s řízením, napájením a chlazením čtyř paralelně pracujících grafických akcelerátorů.

Obrázek 7: Dvě grafické karty Alienware Video Array.

5. Interní sběrnice: shrnutí

V předchozích čtyřech částech seriálu o architekturách počítačů jsme si popsali některé interní sběrnice používané především na osobních počítačích. Při pohledu do minulosti na postupný vývoj sběrnic je možné říci, že se spolu s rostoucím výpočetním výkonem mikroprocesorů a kapacit operačních pamětí měnily i nároky kladené na sběrnice. Především se zvyšovala jejich rychlost, čehož je možné dosáhnout několika způsoby: rozšířením bitové šířky datové části sběrnice, zvýšením hodinové frekvence, přenosem více slov v jednom taktu (nemusí se používat příliš vysoké frekvence hodin) a také vylepšením přenosového protokolu, především o možnosti blokových přenosů dat. Na osobních počítačích se zpočátku používala z dnešního pohledu velmi jednoduchá a pomalá osmibitová sběrnice PC-BUS (XT-BUS) následovaná šestnáctibitovou sběrnicí ISA. Přes relativně neúspěšnou MCA a taktéž v oblasti osobních počítačů nepříliš rozšířenou sběrnici EISA se vývoj ubral dvěma směry – relativně levné a rychlé lokální sběrnice (VESA Local Bus) a univerzální vysokorychlostní sběrnice nezávislé na architektuře mikroprocesoru (PCI a další).

Obrázek 8: Vysokoúrovňová analýza signálů na sběrnici PCI-X.

Vlastnosti lokálních sběrnic, jmenovitě VESA Local Bus, jsou do značné míry závislé na architektuře použitého mikroprocesoru, což prakticky znemožňuje jejich větší rozšíření v delším časovém horizontu. Jejich předností je jednoduchost, a to jak z hlediska řízení sběrnice, tak i implementace řadiče sběrnice (z toho je odvozena i poněkud vyšší rychlost při stejné hodinové frekvenci vycházející z jednoduššího protokolu), ovšem převažují nevýhody – možnost připojení pouze omezeného množství karet, neboť při vyšší logické zátěži dochází ke zhoršení tvaru signálů a tím i k větší citlivosti na šum a vnější rušení, komplikovanější návrh karet určených pro tuto sběrnici, protože výrobci musí počítat se širokým rozsahem frekvencí a také jistá neochota výrobců podporovat lokální sběrnice závislé na jedné konkrétní architektuře mikroprocesoru. Z těchto důvodů byla VESA Local Bus prakticky poslední lokální sběrnicí používanou v osobních počítačích, všechny následující sběrnice byly a jsou univerzální, a to napříč velkým množstvím různých počítačových architektur – například sběrnici PCI můžeme najít jak na deset let starém low-endovém osobním počítači, tak i ve výkonných serverech a průmyslových počítačích.

Sběrnice PCI se (i přes svoji velkou úspěšnost a rozšířenost) pro některé typy zařízení, například grafické karty, řadiče SCSI-320, gigabitové síťové karty atd., stala úzkým hrdlem při přenosu dat, proto opět nastalo dilema – buď bylo možné přejít na rychlejší variantu PCI nebo zachovat stávající PCI (5V, 33 MHz) a přidat k ní speciální port určený pouze pro připojení grafické karty nebo grafického akcelerátoru (tím se ze samotné sběrnice PCI odebere datově nejnáročnější zařízení). První řešení, tj. přechod na 64 bitovou verzi PCI či na PCI-X, se prosadilo na některých modelech serverů, druhé řešení, tj. doplnění PCI o AGP, bylo doménou prakticky všech osobních počítačů vyrobených v posledních cca deseti letech (teprve v minulém roce došlo k výraznější změně). Dnes můžeme být svědky opětovné unifikace a návratu pouze k jednomu typu sběrnice, ke které se připojí všechny karty, bez ohledu na to, zda se jedná o datově náročný grafický akcelerátor či řadič hlemýždí rychlostí se plazícího sériového portu.

Obrázek 9: Konektory některých popsaných interních sběrnic

6. Budoucí vývoj interních sběrnic

Do budoucna je možné očekávat buď další diverzifikaci sběrnic (rychlá – pomalá zařízení), podobně jako tomu bylo u lokální sběrnice VESA Local Bus pracující na jedné základní desce společně s univerzální sběrnicí ISA; popř. i portu AGP a PCI, nebo přechod k odlišné topologii zapojení jednotlivých zařízení, což může být výhodné například u počítačů používajících větší množství mikroprocesorů. Již v předchozích částech tohoto seriálu jsme si řekli, že například některé výkonné grafické stanice firmy SGI (a superpočítače Cray) používají topologii mřížky popř. hyperkostky, podobnou topologii je teoreticky možné použít i u dnes popsané sběrnice PCI-Express. Otázkou ovšem zůstává, zda bude po výkonných několikaprocesorových osobních počítačích poptávka. V oblasti serverů, k nimž se přesouvá stále větší množství aplikací, je situace víceméně jasná, zde se další výpočetní výkon bez problémů využije (serverové aplikace psané v dynamicky typovaných jazycích, servery zpracovávající paralelně velké množství požadavků atd.).

Obrázek 10: Topologie hyperkostky – s každou další dimenzí se počet cest vycházejících z jednoho uzlu zvyšuje pouze o jedničku

Na tomto místě stojí za připomenutí jedna zajímavost – v moderních počítačích se (poněkud s nadsázkou řečeno) téměř výhradně používá sériová forma přenosu dat. Prakticky všechna externí zařízení jsou k počítači připojována přes USB či FireWire („drát ohnivák“), pevné disky a jednotky optických disků používají taktéž sériové rozhraní SATA a karty jsou určeny pro sběrnici PCI-Express. Taková situace ještě v minulosti nikdy nenastala, protože většina sběrnic a rozhraní uvnitř počítače byla založena na paralelním přenosu dat a i vnější vysokorychlostní porty měly osm, šestnáct či třicet dva datových vodičů (paralelní port, vnější SCSI). Ukazuje se, že s rostoucí výkonností čipů a současně i jejich klesající cenou je zavedení sériového přenosu dat výhodné; v případě požadavku na vyšší přenosové rychlosti je možné použít technologii popsanou v prvních kapitolách této části seriálu, tj. několik vzájemně relativně nezávislých sériových (a navíc ještě oboustranných) přenosů.

7. Přenosové rychlosti nejpoužívanějších sběrnic v PC

V následující tabulce jsou vypsány maximální teoretické přenosové rychlosti pro některé typy sběrnic, se kterými jsme se v předchozích částech tohoto seriálu mohli seznámit. Pro úplnost jsem do tabulky zahrnul i některé neoficiální (oficiálně nepodporované či standardem neuváděné) rychlosti; týká se to zejména obou mezních frekvencí u lokální sběrnice VESA Local Bus či sběrnice PCI 3.0 taktované na 133 MHz. Reálné rychlosti jsou snížené vlivem několika faktorů – arbitráží sběrnice, zpracováním přerušení, přenosem adres před zahájením blokových přesunů, přenosem CRC u některých sběrnic atd.

| Označení | Hodinová frekvence | Bitová šířka | Přenosů za takt | Výsledná rychlost | Poznámka |

|---|---|---|---|---|---|

| 8bit ISA (XT Bus) | 4,77 MHz | 8 | 1× | 2,38 MB.s-1 | první takt: adresa, druhý takt: data |

| 16bit ISA (XT Bus) | 6 MHz | 16 | 1× | 6 MB.s-1 | první PC AT |

| 16bit ISA (XT Bus) | 8 MHz | 16 | 1× | 8 MB.s-1 | standardní frekvence |

| 16bit ISA (XT Bus) | 8,33 MHz | 16 | 1× | 8,33 MB.s-1 | standardní frekvence |

| 16bit ISA (XT Bus) | 10 MHz | 16 | 1× | 10 MB.s-1 | nestandardní frekvence |

| 16bit ISA (XT Bus) | 12 MHz | 16 | 1× | 12 MB.s-1 | nestandardní frekvence |

| 16bit ISA (XT Bus) | 16 MHz | 16 | 1× | 16 MB.s-1 | nestandardní frekvence |

| VESA Local Bus | 25 MHz | 32 | 1× | 100 MB.s-1 | odvozeno od frekvence CPU |

| VESA Local Bus | 33 MHz | 32 | 1× | 132 MB.s-1 | odvozeno od frekvence CPU |

| VESA Local Bus | 40 MHz | 32 | 1× | 160 MB.s-1 | odvozeno od frekvence CPU |

| VESA Local Bus | 50 MHz | 32 | 1× | 200 MB.s-1 | odvozeno od frekvence CPU |

| PCI 1.x | 33 MHz | 32 | 1× | 132 MB.s-1 | v desktopových PC standard, 5 V |

| PCI 1.x | 33 MHz | 64 | 1× | 264 MB.s-1 | |

| PCI 2.1 | 66 MHz | 32 | 1× | 264 MB.s-1 | úroveň signálů 3,3 V |

| PCI 2.1 | 66 MHz | 64 | 1× | 532 MB.s-1 | úroveň signálů 3,3 V |

| PCI 3.0 | 133 MHz | 32 | 1× | 532 MB.s-1 | ve stavu návrhu, nahrazeno PCI-X |

| PCI 3.0 | 133 MHz | 64 | 1× | 1066 MB.s-1 | ve stavu návrhu, nahrazeno PCI-X |

| AGP 1× | 66 MHz | 32 | 1× | 266 MB.s-1 | úroveň signálů 3,3 V |

| AGP 2× | 66 MHz | 32 | 2× | 533 MB.s-1 | úroveň signálů 3,3 V |

| AGP 4× | 66 MHz | 32 | 4× | 1066 MB.s-1 | úroveň signálů 1,5 V |

| AGP 8× | 66 MHz | 32 | 8× | 2133 MB.s-1 | úroveň signálů 0,8 V |

| PCI-X | 66 MHz | 64 | 1× | 533 MB.s-1 | zpětně kompatibilní s PCI |

| PCI-X | 133 MHz | 64 | 1× | 1066 MB.s-1 | |

| PCI-X 2.0 | 266 MHz | 64 | 1× | 2133 MB.s-1 | |

| PCI-X 2.0 | 533 MHz | 64 | 1× | 4266 MB.s-1 | |

| PCI Express 1.1 ×1 | 2525 MHz | 1 | 1× | 250 MB.s-1 | přenosová rychlost jedné dráhy |

| PCI Express 1.1 ×2 | 2525 MHz | 2 | 1× | 500 MB.s-1 | každá dráha přenáší data nezávisle na dalších drahách |

| PCI Express 1.1 ×16 | 2525 MHz | 16 | 1× | 4000 MB.s-1 | maximální počet drah ve standardních PC |

| PCI Express 1.1 ×32 | 2525 MHz | 32 | 1× | 8000 MB.s-1 | maximální normou stanovený počet drah |

| PCI Express 2.0 ×1 | 5050 MHz | 1 | 1× | 500 MB.s-1 | přenosová rychlost jedné dráhy |

| PCI Express 2.0 ×2 | 5050 MHz | 2 | 1× | 1000 MB.s-1 | |

| PCI Express 2.0 ×16 | 5050 MHz | 16 | 1× | 8000 MB.s-1 | |

| PCI Express 2.0 ×32 | 5050 MHz | 32 | 1× | 16000 MB.s-1 | více než 6500× rychlejší než první ISA! |

8. Literatura a odkazy na Internetu

- PCI Vendor and Device Lists,

http://www.pcidatabase.com/index.php - Seznam PCI VID/DID,

http://www.pcidatabase.com/reports.php?type=csv - PCI bus pinout,

http://pinouts.ru/Slots/PCI_pinout.shtml - How to recognise a 3.3 Volt PCI slot,

http://www94.web.cern.ch/hsi/s-link/devices/s32pci64/slottypes.html - Computer Bus and BackPlane Design,

http://www.interfacebus.com/Design_Interface_table.html - Applied Micro Circuits Corporation:

S5935 PCI product Data Book,

Applied Micro Circuits Corporation, San Diego, 1999 - Bhatt Ajay V.:

Creating a PCI Express Interconnect,

Technology and Research Labs, Intel Corporation, 2003 - Intel Corporation, Neshati Ramin:

PCI Express Base Specification 1.0a,

Intel Corporation, 2003 - Intel Corporation:

PCI Express documentation

, http://download.intel.com/technology/pciexpress/devnet/docs/pipe2_00.pdf - PCI Express 3.0 Bandwidth: 8.0 Gigatransfers/s,

http://www.extremetech.com/article2/0,1697,2169018,00.asp - Wikipedia CZ: Sběrnice:

http://cs.wikipedia.org/wiki/Sb%C4%9Brnice - Wikipedia CZ: VESA Local Bus,

http://cs.wikipedia.org/wiki/VESA_Local_Bus - Wikipedia EN: VESA Local Bus,

http://en.wikipedia.org/wiki/VESA_Local_Bus - Wikipedia EN: Industry Standard Architecture:

http://en.wikipedia.org/wiki/Industry_Standard_Architecture - Wikipedia EN: Peripheral Component Interconnect,

http://en.wikipedia.org/wiki/Peripheral_Component_Interconnect - Wikipedia EN: PCI Express,

http://en.wikipedia.org/wiki/PCI_Express - Wikipedia EN: PCI-X,

http://en.wikipedia.org/wiki/Pci-x - Advanced Switching for PCI Express Architecture Intel.

http://www.intel.com/technology/pciexpress/devnet/AdvancedSwitching.pdf - Bhatt, Ajay V. „What Is PCI Express?“ Desktop Architecture Labs, Intel.

http://www.intel.com/technology/pciexpress/devnet/docs/WhatisPCIExpress.pdf - Campbell, John. „PCI Express Explained.“ CoolTechZone, August 19, 2004.

http://www.cooltechzone.com/index.php?option=content&task=view&id=506&Itemid=0 - Fisher, Ken. „PCI Express launched in time for the future.“ Ars Technica, June 24, 2004.

http://arstechnica.com/news.ars/post/20040621–3911.html - Fisher, Ken. „Alienware Announces Dual PCI-Express Graphics Subsystem.“ Ars Technica, May 12, 2004.

http://arstechnica.com/news/posts/1084398037.html - „Introduction to PCI Express.“ PC Stats.

http://www.pcstats.com/articleview.cfm?articleid=1087&page=2 - PCI Express FAQ. PCI-SIG.

http://www.pcisig.com/news_room/faqs/faq_express/pciexpress_faq.pdf - „PCI Express Overview.“ Intel, October, 2003. http://www.intel.com/technology/pciexpress/devnet/docs/

PCI-Express-Overview-Oct2003.pdf - Tong, Terren. „A Look at PCI Express.“ Neoseeker, April 21, 2004.

http://www.neoseeker.com/Articles/Hardware/Features/pciexpresstech/ - Wasson, Scott. „NVIDIA's SLI Resurrects GPU Teaming.“ The Tech Report, June 28, 2004.

http://techreport.com/etc/2004q2/nvidia-sli/index.x?pg=1

9. Obsah následující části seriálu

V další části seriálu o architekturách počítačů již opustíme téma interních sběrnic, protože se začneme zabývat problematikou připojení vnějších zařízení k počítačům. Postupně si popíšeme jak některé historické způsoby připojení, například sériový a paralelní port (zejména sériový port má dodnes své oblasti použití), tak i USB a průmyslové externí sběrnice typu I2C apod.