Obsah

1. Procesory RISC v pracovních stanicích a serverech – architektura SPARC

2. Pracovní stanice firmy Sun Microsystems

3. Vlastní architektura mikroprocesorů pro každého výrobce pracovních stanic?

4. Základní informace o mikroprocesorech SPARC

5. Instrukční pipeline mikroprocesorů SPARC

7. Příklad typického použití load delay slotu

8. Formát instrukcí mikroprocesorů SPARC

1. Procesory RISC v pracovních stanicích a serverech – architektura SPARC

V předchozí části seriálu o architekturách počítačů jsme si řekli základní informace o mikroprocesorech MIPS, které byly používány mj. i v grafických stanicích firmy SGI. Dnes můžeme tyto procesory, resp. čipy obsahující licencované jádro MIPS, najít jak ve spotřební elektronice, tak i například v síťových směrovačích. Dnes se budeme zabývat konkurenčními mikroprocesory SPARC, které jsou – stejně jako procesory MIPS – založeny na architektuře RISC. Návrhem mikroprocesorů SPARC se začala zabývat společnost Sun Microsystems přibližně v polovině osmdesátých let minulého století, tj. v době, kdy trhu sice vládly procesory Intel 80×86 a Motorola M68000, které byly postaveny na architektuře CISC, ovšem další výrobci čipů začali poměrně razantně prosazovat své varianty procesorů založených na architektuře RISC. Dokonce se zdálo, že tato architektura za několik let zcela vytlačí ostatní architektury, a to jak v oblasti serverů, tak i v oblasti grafických stanic a osobních počítačů.

Obrázek 1: Pracovní stanice Sun-1, která byla vyráběna ještě předtím, než společnost Sun Microsystems začala ve svých pracovních stanicích používat své mikroprocesory SPARC.

Vývoj se sice v oblasti osobních počítačů nakonec ubíral jiným směrem, což ovšem nebyl ani tak výsledek snah firem, které se na vzniku platformy PC podílely (IBM, Intel, Microsoft), ale spíše důsledek velké konkurence mezi výrobci levných klonů PC, především z Asie. Vraťme se však k mikroprocesorům SPARC. První komerčně nabízená verze těchto procesorů byla dokončena v roce 1987, tj. v době, kdy již existovalo několik konkurenčních RISC procesorů, především již v úvodním odstavci zmíněný MIPS a taktéž HP/PA (PA-RISC). Tato kumulace čipů s podobnými vlastnostmi vedla mj. i k tomu, že pro mikroprocesory s architekturou RISC začaly vznikat kvalitní překladače, které dokázaly efektivně využívat pracovní registry, popř. na některých procesorech optimálně pracovat s minule a předminule popsanými registrovými okny (register windows). Role překladačů je totiž u architektury RISC snad ještě důležitější, než v případě procesorů CISC, zejména kvůli tomu, že jen optimálně přeložený kód dokáže efektivně využít instrukční pipeline (jedním z procesorů, který byl po komerční stránce poměrně neúspěšný právě kvůli absenci kvalitního překladače, je mikroprocesor Intel i860).

Obrázek 2: Mikroprocesor Intel i860, který byl i přes svůj vysoký teoretický výpočetní výkon přesahující 60 MFLOPS po komerční stránce poměrně neúspěšný, především z toho důvodu, že tehdy dostupné překladače dokázaly zkompilovat kód, jehož rychlost mnohdy ani nepřesahovala 10 MFLOPS.

2. Pracovní stanice firmy Sun Microsystems

Společnost Sun Microsystems, která za vznikem mikroprocesorů SPARC stála, měla ve druhé polovině osmdesátých let minulého století na poli unixových pracovních static poměrně výlučnou pozici, protože svým zákazníkům nabízela hned dvě navzájem odlišné řady pracovních stanic. První (výkonnější a taktéž i dražší) série představovaná stanicemi Sun-1, Sun-2 a Sun-3 byla založena na 32bitových mikroprocesorech Motorola M68000, M68010 a M68020. Kromě toho existovala ještě druhá série pracovních stanic představovaná zpočátku počítači Sun386i/150 a Sun386i/250, v nichž byl použit – jak jistě při pohledu na názvy těchto stanic uhádnete – 32bitový mikroprocesor Intel 80386. Tato řada pracovních stanic byla navržena především s ohledem na nízkou cenu a s ní související i nižší výpočetní výkon, než nabízela první řada stanic. Navíc tato levnější řada nabízela i emulaci DOSu spouštěnou přímo z Unixu.

Obrázek 3: Procesorová deska unixové pracovní stanice Sun-1.

Mohlo by se tedy zdát, že lidé ve vedení společnosti Sun Microsystems budou spokojeni s tím, že mají ve svém portfoliu hned dvě navzájem odlišné série poměrně úspěšných unixových pracovních stanic, a nebudou se pokoušet o relativně drahý a taktéž i v mnoha ohledech rizikový vývoj vlastního mikroprocesoru, navíc binárně nekompatibilního jak s řadou mikroprocesorů Motorola M68000, tak i s mikroprocesory Intel 80386. Ve světě operačního systému Unix sice binární nekompatibilita nebyla a dodnes není tak kritická, jako na jiných platformách, přesto však mohla způsobovat problémy. Ve skutečnosti ovšem měli výrobci unixových pracovních stanic (a taktéž výrobci serverů a v neposlední řadě též konstruktéři superpočítačů) hned několik důvodů, proč se alespoň pokusit o prosazení vlastní nové architektury mikroprocesorů. Některé z těchto důvodů, důležitých především z dlouhodobějšího hlediska, se pokusíme vysvětlit v následující kapitole.

Obrázek 4: Deska obsahující grafický subsystém počítače Sun-1. Na pravé straně jsou patrné konektory pro přivedení všech důležitých signálů do monitoru.

3. Vlastní architektura mikroprocesorů pro každého výrobce pracovních stanic?

Prvním důvodem, proč se společnosti srovnatelné se Sun Microsystems s větším či menším úspěchem pokoušeli o vývoj vlastních typů mikroprocesorů, byla snaha o menší závislost na v té době dominantních firmách podnikajících v tomto oboru – společnostech Intel a Motorola. Navíc se výrobci serverů, pracovních stanic i osobních počítačů snažili o větší diverzifikaci svých výrobků oproti konkurenci, což však bylo obtížné, když byly prakticky všechny počítače založeny na podobných mikroprocesorech. Například se uvádí, že v roce 1986 bylo přes 90% osobních počítačů osazeno čipem pocházejícím z firmy Intel a naproti tomu 90% pracovních stanic bylo založeno na některém z procesorů firmy Motorola. Navíc byla výroba mikroprocesorů (po jejich drahém vývoji) relativně levná, protože bylo možné využít nabídek firem vlastnících nové továrny (fabrication plants – fabs) na výrobu čipů. Tyto firmy potřebovaly co nejdříve své továrny zaplatit, takže byly velmi vstřícné ke společnostem, které plánovaly výrobu nových mikroprocesorů, ideálně v několikamilionových sériích.

Obrázek 5: Bezdisková varianta pracovní stanice Sun-2.

Společně s relativně levnými náklady spojenými s vlastní výrobou čipů (nemusela se budovat celá výrobní linka, stačilo „pouze“ uzavřít obchod se specializovaným výrobcem) se v osmdesátých letech minulého století značně zjednodušil i samotný návrh mikroprocesorů i dalších integrovaných obvodů se srovnatelnou složitostí – toto zjednodušení bylo způsobeno existencí specializovaných programů typu CAD umožňujících jak návrh čipu, tak i simulaci jeho chování s přesností na jednotlivé strojové takty. Díky dostupnosti těchto nástrojů se návrh nového typu mikroprocesoru oproti ruční práci jak urychlil, tak i zlevnil (jedním z posledních mikroprocesorů navrhovaných ručně byl pravděpodobně osmibitový mikroprocesor Motorola M6809, částečně též první verze procesoru MIPS-1). Navíc s výrobou čipů mimo společnost, která čip vymyslela a vlastnila na něj veškerá práva, souvisela i možnost licencovat tento čip dalším firmám, což se taktéž u obou dominantních RISCových architektur (MIPS a SPARC) stalo.

Obrázek 6: Pracovní stanice Sun386i se svým vzhledem příliš nelišila od osobních počítačů PC.

4. Základní informace o mikroprocesorech SPARC

V úvodních odstavcích tohoto článku jsme si již řekli, že mikroprocesory SPARC jsou založeny na architektuře RISC. Samotné označení SPARC znamená Scalable Processor ARChitecture, což se postupem času ukázalo být velmi přiléhavým názvem, protože tyto procesory můžeme na jedné straně najít ve vestavěných zařízeních s nízkou spotřebou (například čip microSPARC I má spotřebu pouze 2,5W) a na straně druhé patří některé z těchto procesorů (SPARC64 VIIIfx „Venus“) mezi nejvýkonnější mikroprocesory současnosti. Podívejme se nejprve na strukturu prvního z těchto mikroprocesorů, který byl jednoduše nazvaný SPARC. Tento mikroprocesor z roku 1987 byl založený na architektuře SPARC version 7 (SPARC v7). Architekturou se v tomto kontextu myslí popis instrukční sady, struktury pipeline i počtu pracovních registrů. Jednotliví výrobci čipu SPARC se nedohodli na jejich jednotném pojmenování, proto se budeme často odkazovat spíše na verzi jejich architektury.

Obrázek 7: Unixová pracovní stanice Sun-3.

Původní architektura SPARC v7 byla založena na 32bitové aritmeticko-logické jednotce a sadě 128 pracovních registrů, z nichž však bylo v každý okamžik přístupných pouze 32 registrů. Osm registrů bylo globálních, tj. jejich obsah byl přístupný pro všechny subrutiny, a zbylá sada 24 pracovních registrů se měnila při volání subrutin – tyto registry byly součástí registrového okna popsaného v předchozí části tohoto seriálu. Instrukční pipeline procesorů SPARC měla čtyři řezy, na rozdíl od pěti řezů u mikroprocesorů MIPS. To znamenalo, že instrukce byla provedena ve čtyřech strojových taktech, ovšem v každém strojovém taktu se v procesoru nacházely čtyři rozpracované instrukce, takže špičkový výpočetní výkon odpovídal jedné instrukci provedené v jednom strojovém taktu. Procesor SPARC byl vytvořen s využitím 1,3 mikronové CMOS technologie a při hodinové frekvenci 16,67 MHz jeho reálný výpočetní výkon přesahoval 10 MIPS.

Obrázek 8: Základní deska pracovní stanice Sun-3.

5. Instrukční pipeline mikroprocesorů SPARC

V předchozí části seriálu o architekturách počítačů jsme si popsali instrukční pipeline používanou u mikroprocesorů MIPS. Tato pipeline byla sestavena z pěti řezů a tím pádem se každá instrukce rozkládala na pět postupně prováděných operací. Jedná se o operaci Instruction Fetch (IF), tedy načtení instrukčního kódu z operační paměti, druhou operací je Instruction Decode (ID), tedy dekódování instrukce s výběrem registrů pro provedení operace, třetí operací je Execute (EX), tj. vlastní provedení operace, čtvrtá operace se nazývá Memory Access (MA), což znamená načtení či uložení hodnot do operační paměti a konečně následuje operace pátá Write Back, v níž se vypočtené či načtené hodnoty ukládají zpět do vybraného pracovního registru. Na následujícím schématu je naznačeno, v jakých stavech se nachází pět současně zpracovávaných instrukcí u mikroprocesorů MIPS:

CLK Instrukce: 1. 2. 3. 4. 5. ============================= 01 IF -- -- -- -- 02 ID IF -- -- -- 03 EX ID IF -- -- 04 MA EX ID IF -- 05 WB MA EX ID IF 06 -- WB MA EX ID 07 -- -- WB MA EX 08 -- -- -- WB MA 09 -- -- -- -- WB

Obrázek 9: Mikroprocesor SPARC ve variantě určené pro použití v družicích. Jedná se o verzi se zvýšenou odolností proti záření.

U architektury SPARC je struktura instrukční pipeline poněkud odlišná, protože samotná pipeline je sestavena pouze ze čtveřice řezů, v nichž se provádí operace Instruction Fetch (IF), Execute (EX), Memory Access (MA) a Write Back (WB). Díky tomu, že je vynechána operace Instruction Decode, je možné, aby druhá instrukce v pipeline využila výsledky vypočtené v předchozí instrukci (bypass), takže v tomto případě nedojde k vložení zpožďovacích „prázdných“ slotů (delay slotů). Na následujícím schématu je naznačeno, v jakém stavu se nachází čtveřice instrukcí v instrukční pipeline za předpokladu, že procesor nepoužil žádný delay slot:

CLK Instrukce: 1. 2. 3. 4. ========================== 01 IF -- -- -- 02 EX IF -- -- 03 MA EX IF -- 04 WB MA EX IF 05 -- WB MA EX 06 -- -- WB MA 07 -- -- -- WB

Obrázek 10: Mikroprocesory UltraSPARC jsou pokračovateli původního 32bitového mikroprocesoru SPARC.

6. Load delay sloty

V předchozí kapitole jsme si řekli, že v některých případech je možné využít výsledek předchozí instrukce prakticky ihned instrukcí následující, aniž by muselo dojít k pozastavení provádění následující instrukce o jeden strojový takt. Tento bypass lze ovšem použít pouze v případě, že první instrukce inkriminované dvojice je instrukcí aritmetickou či logickou, tj. instrukcí prováděnou s obsahem pracovních registrů (ovšem existence bypassu je vyvážena poněkud složitějším zapojením mikroprocesoru).

Obrázek 11: Ultra SPARC II – další v minulosti velmi často používaný mikroprocesor s architekturou RISC

Zdroj: Wikipedia.

Pokud se však jedná o instrukci typu LOAD (LD), je situace poněkud složitější, protože se načtení hodnoty z operační paměti provádí až ve třetí operaci/fázi (Memory Access – MA). V případě, že při provádění instrukcí dojde k tomu, že za instrukcí typu LOAD (LD) následuje instrukce, která načítanou hodnotu ihned využívá, vkládá procesor mezi obě instrukce takzvaný load delay slot, který provádění druhé instrukce o jeden takt pozdrží.

Obrázek 12: Interní struktura novějších verzí mikroprocesorů s architekturou SPARC, na níž můžeme najít jak moduly pro práci s celými čísly, tak i moduly FPU.

7. Příklad typického použití load delay slotu

Podívejme se na jednoduchý příklad, v němž je v první instrukci načtena hodnota pracovního registru R11 z operační paměti a ihned poté se s načtenou hodnotou provádí aritmetická operace součtu (add):

ld %r10+offset,%r11 [load to r11] add %r11,%r12,%r13 [add r11+r12]

Procesor SPARC v tomto případě nemůže provést fázi Execute (EX) u druhé instrukce, protože se přesně ve stejný okamžik teprve načítá jeden z operandů této instrukce z operační paměti ve fázi Memory Access (MA) první instrukce ve dvojici. Následující schéma by tedy vedlo k chybné funkci:

CLK Instrukce: 1. 2. ==================== 01 IF -- 02 EX IF 03 MA EX - zde dojde k načtení obsahu registru R11 04 WB MA a současně se má provést EX ve druhé instrukci 05 -- WB

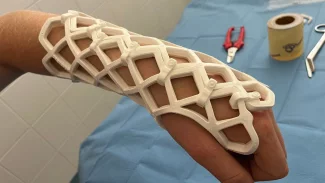

Obrázek 13: Mikroprocesor UltraSparc IIe („Hummingbird“). Jedná se o variantu určenou především do vestavěných zařízení.

Z tohoto důvodu se mezi obě instrukce vloží takzvaný delay slot, takže je provedení druhé instrukce o jeden strojový takt posunuto:

CLK Instrukce: 1. 2. ==================== 01 IF -- -- 02 EX D -- 03 MA D IF - zde dojde k načtení obsahu registru R11 04 WB D EX - druhá instrukce již zná nový obsah registru R11 05 -- D MA 06 -- -- WB

Obrázek 14: Mikroprocesor UltraSparc IIi („Sabre“).

8. Formát instrukcí mikroprocesorů SPARC

Procesory s architekturou SPARC používají, podobně jako minule popsané procesory MIPS, instrukční sadu s instrukcemi, jejichž délka je konstantní – 32 bitů. Podle rozdělení oněch třiceti dvou bitů na jednotlivá bitová pole rozeznáváme pět typů formátů instrukcí. Nejjednodušší je instrukce skoku, v níž je použita 30bitová konstanta, která je posunuta o dva bity doleva, takže výsledkem tohoto výpočtu je 32 bitová adresa se zarovnáním na čtyři bajty:

+-------------------------------------------------------------+ | 01 | 30 bit constant | +-------------------------------------------------------------+

Druhým typem instrukcí jsou instrukce pro provádění podmíněných skoků, protože procesory SPARC mohou skok provést na základě několika podmínek, na rozdíl od procesorů MIPS, kde bylo možné pouze provádět porovnání dvou hodnot na rovnost či nerovnost. Kromě bitů představujících kód podmínky (cond) se v bitovém poli nachází i operand, s nímž je provedeno porovnání (op2) a konstanta, z níž se po posunu o dva bity doleva vypočte relativní adresa skoku:

+-------------------------------------------------------------+ | 00 |a(1)| cond(4) | op2(3)| 22 bit constant | +-------------------------------------------------------------+

Obrázek 15: Mikroprocesor Fujitsu SPARC64 VIIIfx („Deta“).

Třetí formát je použit instrukcí sethi pro načtení horních 22 bitů do libovolného viditelného pracovního registru určeného bitovým polem rd. Nižších deset bitů lze nastavit například instrukcí or (způsob načtení 32bitové konstanty je tedy podobný situaci, která panovala u mikroprocesorů MIPS):

+-------------------------------------------------------------+ | 00 |rd (5) |100| 22 bit constant | +-------------------------------------------------------------+

Obrázek 16: Jeden z nejvýkonnějších procesorů současnosti – SPARC64 VIIIfx (kódové jméno „Venus“) s osmi jádry a výkonem dosahujícím 128 GFLOPS.

Poslední dva formáty instrukcí jsou použity u všech aritmetických i logických instrukcí, tj. u instrukcí se dvěma operandy a specifikací registru, do nějž se má výsledek operace uložit. Index tohoto registru je uložen v poli rd, první zdrojový registr v poli rs a druhý operand buď v poli rs2 (pokud se jedná o pracovní registr), nebo v poli const (pokud se jedná o konstantu). Kód prováděné operace je uložen v bitovém poli op3:

+-------------------------------------------------------------+ | 10 | rd (5) | op3 (6) | rs1 (5) |0| unused (8) | rs2 (5) | +-------------------------------------------------------------+

+-------------------------------------------------------------+ | 11 | rd (5) | op3 (6) | rs1 (5) |1| signed 13 bit const | +-------------------------------------------------------------+

Tento formát je využit i u instrukcí typu LOAD a STORE, zde se ovšem navíc využívá frame pointer, jehož funkci si vysvětlíme příště.

9. Odkazy na Internetu

- SPARC Pipelining

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/pipelining.html - SPARC Instruction

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/inst_set.html - History of SPARC systems 1987 to 2010

http://www.sparcproductdirectory.com/history.html - Sun-1 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-1 - Sun-2 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-2 - Sun-3 (Wikipedia)

http://en.wikipedia.org/wiki/Sun-3 - Sun386i (Wikipedia)

http://en.wikipedia.org/wiki/Sun386i - Sun 386i/250

http://sites.inka.de/pcde/site/sun386i.html - SPARC Instruction Set

http://www.academic.marist.edu/~jzbv/architecture/Projects/S2002/SPARC/inst_set.html - MIPS Architecture Overview

http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/mips.html - MIPS Technologies R3000

http://www.cpu-world.com/CPUs/R3000/ - CPU-collection: IDT R3010 FPU

http://www.cpu-collection.de/?tn=0&l0=co&l1=IDT&l2=R3010+FPU - The MIPS R2000 Instruction Set

http://suraj.lums.edu.pk/~cs423a05/Reference/MIPSCodeTable.pdf - Maska mikroprocesoru RISC 1

http://www.cs.berkeley.edu/~pattrsn/Arch/RISC1.jpg - Maska mikroprocesoru RISC 2

http://www.cs.berkeley.edu/~pattrsn/Arch/RISC2.jpg - The MIPS Register Usage Conventions

http://pages.cs.wisc.edu/~cs354–2/beyond354/conventions.html - C.E. Sequin and D.A.Patterson: Design and Implementation of RISC I

http://www.eecs.berkeley.edu/Pubs/TechRpts/1982/CSD-82–106.pdf - Berkeley RISC

http://en.wikipedia.org/wiki/Berkeley_RISC - Great moments in microprocessor history

http://www.ibm.com/developerworks/library/pa-microhist.html - Microprogram-Based Processors

http://research.microsoft.com/en-us/um/people/gbell/Computer_Structures_Principles_and_Examples/csp0167.htm - Great Microprocessors of the Past and Present

http://www.cpushack.com/CPU/cpu1.html - A Brief History of Microprogramming

http://www.cs.clemson.edu/~mark/uprog.html - Architecture of the WISC CPU/16

http://www.ece.cmu.edu/~koopman/stack_computers/sec4_2.html - Zásobníkový procesor WISC CPU/16 (Root.CZ)

http://www.root.cz/clanky/programovaci-jazyk-forth-a-zasobnikove-procesory-16/#k03 - Writable instruction set, stack oriented computers: The WISC Concept

http://www.ece.cmu.edu/~koopman/forth/rochester87.pdf - The Great CPU List: Part X: Hitachi 6301 – Small and microcoded (1983)

http://jbayko.sasktelwebsite.net/cpu2.html#Sec2Part10 - What is RISC?

http://www-cs-faculty.stanford.edu/~eroberts/courses/soco/projects/2000–01/risc/whatis/ - RISC vs. CISC

http://www-cs-faculty.stanford.edu/~eroberts/courses/soco/projects/2000–01/risc/risccisc/ - RISC and CISC definitions:

http://www.cpushack.com/CPU/cpuAppendA.html - The Evolution of RISC

http://www.ibm.com/developerworks/library/pa-microhist.html#sidebar1 - SPARC Processor Family Photo

http://thenetworkisthecomputer.com/site/?p=243 - SPARC: Decades of Continuous Technical Innovation

http://blogs.oracle.com/ontherecord/entry/sparc_decades_of_continuous_technical - The SPARC processors

http://www.top500.org/2007_overview_recent_supercomputers/sparc_processors - Maurice V. Wilkes Home Page

http://www.cl.cam.ac.uk/archive/mvw1/ - Papers by M. V. Wilkes (důležitá je především jeho práce číslo 35)

http://www.cl.cam.ac.uk/archive/mvw1/list-of-papers.txt - Microprogram Memory

http://free-books-online.org/computers/advanced-computer-architecture/microprogram-memory/ - First Draft of a report on the EDVAC

http://qss.stanford.edu/~godfrey/vonNeumann/vnedvac.pdf - Introduction to Microcontrollers

http://www.pic24micro.com/cisc_vs_risc.html - Reduced instruction set computing (Wikipedia)

http://en.wikipedia.org/wiki/Reduced_instruction_set_computer - MIPS architecture (Wikipedia)

http://en.wikipedia.org/wiki/MIPS_architecture - Very long instruction word (Wikipedia)

http://en.wikipedia.org/wiki/Very_long_instruction_word - Classic RISC pipeline (Wikipedia)

http://en.wikipedia.org/wiki/Classic_RISC_pipeline - R2000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R2000_(microprocessor) - R3000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R3000 - R4400 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R4400 - R8000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R8000 - R10000 Microprocessor (Wikipedia)

http://en.wikipedia.org/wiki/R10000 - SPARC (Wikipedia)

http://en.wikipedia.org/wiki/Sparc - CPU design (Wikipedia)

http://en.wikipedia.org/wiki/CPU_design - Control unit (Wikipedia)

http://en.wikipedia.org/wiki/Control_unit - Microcode (Wikipedia)

http://en.wikipedia.org/wiki/Microcode - Microsequencer (Wikipedia)

http://en.wikipedia.org/wiki/Microsequencer - Maurice Wilkes (Wikipedia)

http://en.wikipedia.org/wiki/Maurice_Wilkes - Micro-operation (Wikipedia)

http://en.wikipedia.org/wiki/Micro-operation