Obsah

1. Technologie grafických stanic a serverů firmy SGI

5. Topologie uzlů použitá u serverů Origin 200/2000

7. Obsah dalšího pokračování seriálu

1. Technologie grafických stanic a serverů firmy SGI

V předchozí části seriálu o architekturách počítačů jsme si popsali jedno technologické řešení vyvinuté firmou SGI (Silicon Graphics Inc.) pro podporu rychlého zobrazování prostorových scén uložených v hraniční reprezentaci (tělesa ve scénách jsou tedy popsána svým povrchem – hranicí mezi vnitřkem a vnějškem tělesa). Jednalo se o grafický subsystém nazvaný Stellar GS2000, jehož funkční části (zejména vektorový procesor, rasterizační jednotku a framebuffer) můžeme, i když v poněkud inovované podobě, nalézt i v prakticky všech moderních grafických akcelerátorech. Dnes si popíšeme další, z dnešního pohledu velmi důležitou technologii navrženou firmou SGI – jedná se o architekturu NUMA, což je zkratka z plného názvu Non-Uniform Memory Access. Tímto názvem je naznačeno, jakým způsobem je provedeno vzájemné uspořádání a propojení procesorů (popř. procesorových jader), vyrovnávacích pamětí a paměti operační.

Obrázek 1: Blokový diagram grafického akcelerátoru Stellar GS2000 popsaného v předchozí části tohoto seriálu.

2. Architektury SMP a NUMA

Architektura NUMA byla firmou SGI navržena za účelem propojení velkého množství procesorů, které mezi sebou musí určitým způsobem komunikovat, tj. sdílet data. Při použití malého množství procesorů (2 až 8) je možné použít takzvaný symetrický multiprocessing – SMP (Symmetric Multiprocessing), v němž existuje pouze jedna hlavní (operační) paměť a procesory k této paměti přistupují přes vhodnou propojovací strukturu, která obsahuje i arbitr. Na bázi SMP byly vystavěny i první víceprocesorové osobní počítače a jednodušší servery. Vždy se však jednalo o propojení dvojic, čtveřic procesorů a v maximální konfiguraci osmi procesorů (to je však již velmi neefektivní řešení). Blokové schéma architektury SMP je naznačeno na druhém obrázku.

Obrázek 2: Blokové schéma architektury SMP. Každý procesor je propojen s vlastní vyrovnávací pamětí (která může být rozdělena na vyrovnávací paměť určenou pro data a vyrovnávací paměť pro instrukce). Vyrovnávací paměti jsou napojeny na interní sběrnici popř. přepínací síť, která zajišťuje řízení přenosu dat mezi těmito paměťmi a pamětí operační. Na přepínací síť bývají taktéž zapojeny některá rychlá vstupně/výstupní zařízení (například grafický akcelerátor) či řadiče sběrnic (PCI).

Architektura SMP je poměrně jednoduchá, proto je také snadná a samozřejmě i levná její implementace. Potíže však nastávají při připojení většího množství procesorů. Už při čtyřech současně běžících procesorech se ukazuje, že propojovací struktura se stává úzkým hrdlem této architektury, protože i přes mnohdy velikou kapacitu vyrovnávacích pamětí (cache) nastávají kolize při přístupu do hlavní paměti, kdy na sebe jednotlivé procesory musí čekat (blíže viz Amdahlův zákon, který mj. ukazuje, do jaké míry může i malá sekvenčně prováděná část programu zneefektivnit použití většího množství procesorů).

Obrázek 3: Amdahlův zákon vyjádřený graficky. S rostoucím počtem procesorů (popř. procesorových jader) neroste výpočetní výkon celého počítače lineárně, protože určitou část úlohy není možné provádět paralelně (například se jedná o vstup či výstup dat, přístup ke sdílenému prostředku atd.). Při použití architektury SMP však může snaha o souběžný přístup k operační paměti způsobit průběh naznačený červenou křivkou – pro velké množství procesorů je nejvíce procesorového času „promrháno“ arbitráží společné sběrnice.

3. Princip architektury NUMA

Tuto poměrně vážnou nevýhodu symetrického multiprocesingu odstraňuje architektura NUMA, v níž se zavádí namísto jednoduché lineární propojovací struktury složitější topologie, jako je mřížka, krychle, hyperkrychle, torus nebo hypertorus. V uzlech této topologické sítě se nacházejí jednotlivé procesory (popř. procesorová jádra nebo jejich dvojice – viz další kapitoly), operační paměť a další zařízení, mimo jiné i grafický akcelerátor či dokonce větší množství spolupracujících grafických akcelerátorů. Ty jsou z tohoto hlediska zcela rovnocenné procesorům, na rozdíl od architektury PC. Nejdůležitější odlišností architektury NUMA je však již zmíněné rozdělení operační paměti mezi jednotlivé uzly. Jedná se vlastně o zobecněné schéma DSM (Distributed Shared Memory neboli distribuovaná sdílená paměť), které s sebou přináší nutnost rozdělení informací mezi jednotlivé části operační paměti umístěné v jednotlivých uzlech.

Obrázek 4: Architektura moderní pracovní stanice rozšiřující „klasickou“ architekturu osobních počítačů, ve které se sice nachází trojice CPU (či výpočetních jader) s vyrovnávacími paměťmi první úrovně, ovšem jak operační paměť, tak i vyrovnávací paměti druhé úrovně jsou již pro všechny CPU společné, což tvůrce této architektury vedlo k nutnosti vytvoření velmi rychlých komunikačních kanálů mezi CPU, North Bridgem a operační pamětí. Netřeba dodávat, že škálovatelnost tohoto řešení je poměrně malá, řádově se jedná o jednotky CPU. Povšimněte si, že oproti druhému obrázku, na němž je zobrazeno principiální schéma architektury SMP zde došlo k jedné poměrně významné změně – zatímco vyrovnávací paměť první úrovně je pro každé výpočetní jádro samostatná (a rozdělená na datovou a instrukční cache), je vyrovnávací paměť druhé úrovně již společná pro všechna tři jádra, stejně jako blok operační paměti.

Důležité je, že určitý blok paměti se může v počítači s architekturou NUMA vyskytovat současně ve více kopiích (uložených v jednotlivých uzlech), přičemž je pomocí komunikačního protokolu zajišťována konzistence informací v jednotlivých blocích. Pokud některý z procesorů zapíše do tohoto bloku data, je zajištěno, aby v případě potřeby existovala kopie tohoto bloku i v dalších uzlech, ale pouze v případě, že tento uzel data skutečně potřebuje číst (kopie se tedy provádí až v době, kdy je to nezbytně nutné). Podobným způsobem je zajištěn i souběžný zápis dat do jednoho bloku více procesory současně, což je jedna z mála operací, při níž na sebe procesory musí čekat (souběžné čtení jednoho bloku více procesory nepřináší žádné problémy, což mj. zahrnuje i čtení jednotlivých instrukcí z kódových segmentů). Efektivita architektury NUMA je tedy do značné míry závislá na algoritmu, který je použit pro distribuci a vzájemné synchronizaci obsahů jednotlivých paměťových bloků.

4. Servery Origin 200/2000

Firma SGI použila architekturu NUMA u mnoha svých počítačů, mj. také při návrhu serverů Origin 200 a Origin 2000. U těchto strojů je použita mírná modifikace uzlů, ve kterých je namísto jediného procesoru zapojena vždy dvojice procesorů – viz též pátý obrázek. Ke každému procesoru přináleží i několik vyrovnávacích pamětí – instrukční vyrovnávací paměť (na následujícím obrázku je označena symbolem I-c, který vznikl ze sousloví „instruction cache“), datová vyrovnávací paměť (na obrázku je označena symbolem D-c, neboli „data cache“) a část sdílené paměti (označena symbolem S-cache). V následujících kapitolách si řekneme, jaká topologie propojení uzlů je u serverů Origin 200/2000 použita a jaké významné vlastnosti tato topologie přináší.

Obrázek 5: Struktura jednoho uzlu použitého u serverů Origin 200/2000. Každý uzel obsahuje hub zajišťující komunikaci s okolními uzly (CrayLink) i vybraným zařízením (XIO) a dvojici procesorů, z nichž každý má k dispozici instrukční vyrovnávací paměť, datovou vyrovnávací paměť a sdílenou paměť (přesněji. paměťový modul obsahující část sdílené paměti).

5. Topologie uzlů použitá u serverů Origin 200/2000

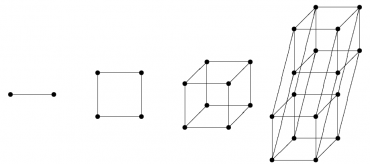

U serverů Origin 200/2000 se pro propojování jednotlivých uzlů používá topologie sítě založená na hyperkrychli (hypercube). Hyperkrychle vzniká zobecněním plošného čtverce či prostorové krychle do obecně libovolného počtu dimenzí. Ve vrcholu plošného čtverce se stýkají dvě hrany, ve vrcholu třírozměrné krychle tři hrany, ve vrcholu hyperkrychle ve čtyřech dimenzích čtyři hrany atd. Podle počtu uzlů je vhodně zvolena dimenze hyperkrychle (1 až 7, praktický limit je roven pěti), která se v běžných případech pohybuje od dvou uzlů do 128 uzlů. Tento počet sice nepředstavuje teoretické maximum, ale s dalším přidáváním uzlů se poměrně značným způsobem zvyšuje počet hran, které se stýkají v jednom vrcholu hyperkrychle, čímž se také prodlužuje předávání dat mezi jednotlivými uzly (složité routování dat, komplikované přepínače atd.). Na šestém obrázku je ukázána propojovací topologie hyperkrychle pro několik základních konfigurací serverů Origin 200/2000. Každý uzel na obrázku přitom obsahuje dva procesory (například typu R10000 – viz následující dvě kapitoly) se svými vyrovnávacími paměťmi.

Obrázek 6: Propojovací topologie hyperkrychle použité u serverů Origin 200/2000.

Velkou předností použité propojovací topologie propojování výpočetních uzlů u serverů Origin 200/2000, je vysoká škálovatelnost, která umožňuje efektivní použití až několika set procesorů. Tyto procesory se mohou využít například pro vykreslování trojrozměrných scén metodou raytracingu, neboť tato metoda je takřka ideálně paralelizovatelná (samozřejmě až na rostoucí paměťovou složitost). Další často používanou možností je připojení několika grafických akcelerátorů pro urychlení vykreslování trojrozměrné grafiky v hraniční reprezentaci.

Obrázek 7: Čtyřrozměrná hyperkrychle obsahující 16 uzlů, která dovoluje při jejím využití v serverech Origin současně provozovat až 32 procesorů (dva procesory v každém uzlu). Každý uzel sousedí pouze se čtyřmi dalšími uzly, takže směrovače nejsou příliš složité. Maximální cesta, kterou musí data urazit při komunikaci, je rovna čtyřem „skokům“ (u třídimenzionální krychle jde o tři skoky).

6. Procesor R10000

V některých superpočítačích firmy SGI se pro realizaci jednotlivých výkonných uzlů používaly procesory typu R10000, které byly navrženy s ohledem na co největší výpočetní výkon (zajištěný mj. i použitím superskalární architektury, predikce skoků, vykonáváním instrukcí mimo pořadí atd.). Tyto procesory nepracovaly v naprosté většině konfigurací samostatně (jak tomu bylo donedávna u prakticky všech osobních počítačů vybavených mikroprocesory s jedním jádrem), ale zapojovaly se do větších celků realizovaných pomocí topologie popsané v předchozích kapitolách – většinou se jednalo o hyperkrychle o třech až pěti dimenzích, takže celkový počet procesorů nainstalovaných do jednoho superpočítače mohl dosahovat poměrně vysokých hodnot (64 procesorů zdaleka nebylo neobvyklé číslo). Pojďme si nyní říci, jakým způsobem bylo dosaženo poměrně vysokého výpočetního výkonu těchto procesorů.

Obrázek 8: Funkční moduly procesoru R10000.

Procesor R10000 neobsahuje pouze jedinou aritmeticko-logickou jednotku, ale pět vzájemně nezávislých výpočetních jednotek. Jedná se o sčítačku adres (jejíž použití je zřejmé – indexové adresování, adresa zadaná pomocí báze a offsetu, adresování parametrů uložených na zásobník atd.), ALU určenou pro provádění všech aritmetických a logických operací s celými čísly či hodnotami reprezentovanými ve formátu pevné řádové čárky (FX – Fixed Point), druhou ALU specializovanou pouze na sčítání a násobení (celých čísel či čísel s pevně umístěnou řádovou čárkou) a konečně dvě jednotky určené pro provádění základních aritmetických operací s čísly reprezentovanými ve formátu pohyblivé řádové čárky (FP – Floating Point). Tyto dvě jednotky dokázaly provádět operace sčítání, násobení a výpočet druhé odmocniny (tato operace je důležitá v některých grafických algoritmech, například při výpočtech délek vektorů či vzdáleností bodů v ploše i prostoru).

Obrázek 9: Takto vypadá procesor R10000 při pohledu mikroskopem. Jednotlivé funkční moduly (bloky) jsou obarveny.

Jedná se o procesor typu RISC založený na známé a dodnes populární architektuře MIPS, což mj. znamená, že jeho instrukční sada obsahuje základní sadu instrukcí, které většinou pracují s hodnotami uloženými v pracovních registrech. Jedinou výjimkou jsou (kromě skoků a několika specializovaných instrukcí) instrukce typu LOAD a STORE, které umožňují načítat popř. ukládat hodnoty z a do operační paměti. Procesor má superskalární architekturu, což znamená, že v jednom cyklu může (současně) zpracovávat až čtyři instrukce. Procesor taktéž obsahuje jednotku pro výběr instrukcí mimo pořadí (out-of-order execution), která dokáže zajistit přerozdělení instrukcí (uložených v instrukčních frontách přímo na procesoru) s ohledem na optimální vytížení jednotlivých výpočetních jednotek. S jednotkou out-of-order execution souvisí též modul provádějící mapování registrů, který se uplatní například ve chvíli, kdy je by docházelo ke kolizím při čtení a zápisu do stejného registru (což by znamenalo, že by se muselo čekat do dokončení předcházející instrukce).

Obrázek 10: Na některých sériích procesoru R10000 se při pohledu mikroskopem objevila tato pěkná SPZka :-)

Navíc obsahoval procesor R10000 dvoubitový prediktor skoků (viz vysvětlivka u obrázku číslo 11) a spekulativní provádění skoků, což tvůrcům tohoto procesoru umožnilo implementovat poměrně dlouhé pipeline s velkým počtem řezů aniž by často docházelo k nutnosti vyprázdnění celé pipeline v důsledku toho, že se kvůli provedení (či naopak neprovedení) nějakého skoku začaly zpracovávat instrukce ve špatné programové větvi. Díky všem výše zmíněným technologiím bylo možné již v roce 1994 vyrobit poměrně levný procesor nabízející relativně slušný výpočetní výkon 784 MIPS a 392 MFLOPS s rychlostí přenosu dat mezi mikroprocesorem a vyrovnávací pamětí, která dosahovala (při přenosu celých bloků, nikoli jednotlivých slov) hodnot 1,2 GB/sec.

Obrázek 11: Přechody mezi čtyřmi stavy dvoubitového prediktoru skoků. V závislosti na tom, zda je podmíněný skok na základě vyhodnocení podmínky proveden (T – taken) či neproveden (NT – not taken) může dvoubitový prediktor skoků přejít do jednoho ze svých čtyř vnitřních stavů, na jejichž základě se procesor rozhoduje, která programová větev se začne dopředu zpracovávat. Pokud se prediktor splete (tj. ve skutečnosti se má provést druhá větev než ta, kterou předpověděl), již zpracované instrukce (a hodnoty registrů) se musí zahodit a začít se zpracováváním správné větve, což s sebou samozřejmě nese zpoždění v provádění programu. Pokud se prediktor nachází v prvních dvou stavech, zpracovává se ta větev programu, jejíž instrukce jsou umístěny za příkazem skoku, u druhých dvou stavů naopak ty instrukce, které se nachází na adrese, kam se (pravděpodobně) skok provede. Uvádí se, že pravděpodobnost správného odhadu, zda se skok provede či neprovede, překračuje u dvoubitového prediktoru hodnotu 90% (některé zdroje uvádí dokonce úspěšnost správného odhadu 95% či dokonce 97%).

7. Obsah dalšího pokračování seriálu

V následující části seriálu o architekturách počítačů si popíšeme další technologie navržené a samozřejmě taktéž realizované firmou SGI. Budeme se zabývat především popisem architektur Onyx 2 (s velmi výkonným grafickým subsystémem), Onyx 3000 a v neposlední řadě také architektury Reality Engine, Jedná se o jedny z nejvýznamnějších a taktéž nejvýkonnějších superpočítačů orientovaných na práci s grafikou, které (každý ve své době) znamenaly naprostou špičku mezi grafickými systémy. Pro ilustraci možností těchto strojů uvedu několik čísel: grafický subsystém architektury Onyx 3000, nabízené od roku 2002, dokázal vykreslit až 300 milionů trojúhelníků za sekundu a vyplnit 7,7 miliard pixelů/fragmentů za tutéž časovou jednotku.

Obrázek 12: Systém Silicon Graphics Onyx 2.

8. Odkazy na Internetu

- Amdahl's law

http://en.wikipedia.org/wiki/Amdahl%27s_law - Hypercube

http://en.wikipedia.org/wiki/Hypercube - R10000

http://en.wikipedia.org/wiki/R10000 - NUMA: Frequently Asked Questions

http://lse.sourceforge.net/numa/faq/ - NUMA (Numa Support in Linux)

http://oss.sgi.com/projects/numa/ - Symmetric multiprocessing

http://en.wikipedia.org/wiki/Symmetric_multiprocessing - Non-Uniform Memory Access

http://en.wikipedia.org/wiki/Non-Uniform_Memory_Access - Northbridge (computing)

http://en.wikipedia.org/wiki/Northbridge_(computing) - Southbridge (computing)

http://en.wikipedia.org/wiki/Southbridge_(computing) - Carrier sense multiple access with collision detection

http://en.wikipedia.org/wiki/Carrier_sense_multiple_access_with_collision_detection - Intel i740

http://en.wikipedia.org/wiki/Intel740 - Intel i740 Datasheet

ftp://download.intel.com/support/graphics/intel740/29061902.pdf - Intel740™ Graphics Accelerator P854 Hardware

ftp://download.intel.com/support/graphics/intel740/29062202.pdf - S3 Savage

http://en.wikipedia.org/wiki/S3_Savage - Savage (S3)

http://www.economy-point.org/s/savage-s3.html - 3dfx Interactive

http://en.wikipedia.org/wiki/3dfx_Voodoo_Graphics - Intel 860@cpu-collection

http://www.cpu-collection.de/?l0=co&l1=Intel&l2=i860 - S3 Graphics

http://www.s3graphics.com/en/index.aspx - TSENG ET6000 Performance Page

http://dani75.tripod.com/TSENG.htm - Tseng Labs Ships ET6000 Advanced Graphics Chip, Announces Additional Manufacturing Sources

http://www.encyclopedia.com/doc/1G1–18088868.html - CyberMax chooses Tseng Labs' ET6000 Graphics and Video Controller for Max and ProMax Series PCs

http://findarticles.com/p/articles/mi_m0EIN/is_1996_Oct9/ai_18754932/ - Intel i860

http://en.wikipedia.org/wiki/Intel860 - Intel i860 64-Bit Microprocessor

http://www.microprocessor.sscc.ru/i860.html - 25 Microchips That Shook the World

http://www.synbio.org.uk/scientific-computing-news/1351.html - Sprite (computer graphics)

http://en.wikipedia.org/wiki/Sprite_(computer_graphics) - Sprite (počítačová grafika)

http://cs.wikipedia.org/wiki/Sprite_(počítačová_grafika) - Wikipedia: Video Display Controller

http://en.wikipedia.org/wiki/Video_Display_Controller - 3dfx Voodoo1 PCI

http://www.v3info.de/english/html/v1.shtml - Glide 2.2 Programming Guide

http://www.gamers.org/dEngine/xf3D/glide/glidepgm.htm - Glide API

http://en.wikipedia.org/wiki/Glide_API - The MIPS R10000 Superscalar Microprocessor

http://portal.acm.org/citation.cfm?id=623999