Obsah

1. Instrukční sada osmibitových mikrořadičů AVR

2. Časování instrukcí na mikrořadičích AVR a rozdělení instrukcí do kategorií

3. Instrukce provádějící operaci s jedním nebo dvěma pracovními registry

6. Podmíněné instrukce typu SKIP

7. Práce s jednobitovými hodnotami

8. Adresování používané u instrukcí typu LD (Load) a ST (Store)

1. Instrukční sada osmibitových mikrořadičů AVR

V předchozí části seriálu o architekturách počítačů jsme si stručně popsali historii vzniku osmibitových mikrořadičů AVR vyráběných firmou Atmel. Víme již, že tyto mikrořadiče jsou založeny na kombinaci dvou architektur – Harvardské architektury, díky níž je například možné mít oddělenou paměť pro program (typu Flash) a paměť pro data (typu SRAM) a taktéž architektury RISC, z níž si konstruktéři mikrořadičů AVR vzali především ideu jednoduchých strojových instrukcí prováděných v jednom strojovém cyklu (což mj. zjednodušuje i obvodové řešení reakce na vznik přerušení) a taktéž vysoký počet pracovních registrů (16 či 32), s nimiž mohou být instrukce prováděny. Díky těmto vlastnostem se mikrořadiče AVR staly krátce po svém uvedení na trh velmi oblíbené, o čemž mj. svědčí i jejich časté používání v různých kitech, například ve slavném Arduinu (jímž se na stránkách Rootu.cz zabývá především kolega Martin Malý) nebo ve velmi povedené herní konzoli Uzebox, kterou si popíšeme příště.

Obrázek 1: Instrukční sada osmibitového mikrořadiče M68HC05.

(Zdroj: Freescale Semiconductor, Ltd. MC68HC05B6/D Rev. 4.1 08/2005)

Pojďme se nyní seznámit se základy instrukčního souboru osmibitových mikrořadičů AVR. Nebude se jednat o úplný popis se všemi podrobnostmi, protože ten lze najít v materiálech firmy Atmel. Řekneme si pouze, jaký je formát instrukcí a jak (a zda vůbec) můžeme najít nějaké paralely mezi architekturou čipů AVR a mikrořadiči, jejichž popisem jsme se již zabývali v předchozích článcích (8048, 8051, PIC a 68HCxx). Některé údaje o instrukční sadě jsme si již řekli minule. Víme již, že instrukce nejsou kódovány po bajtech, tedy tak, jak je tomu zejména u čipů 8048, 8051 či 68HCxx, kde se vždy v prvním bajtu nachází kód instrukce a v bajtech následujících potom konstanty, rozšiřující kódy některých instrukcí či adresy. Namísto toho má v případě mikrořadičů AVR naprostá většina instrukcí šířku šestnáct bitů a pouze několik málo instrukcí bylo rozšířeno na 32 bitů. Instrukce jsou načítány po šestnáctibitových slovech v jednom strojovém taktu, což je jedna z předností Harvardské architektury.

Obrázek 2: Instrukční sada osmibitového mikrořadiče 68HC08.

(Zdroj: Technical Data – MC68HC08AB16A, Freescale Semiconductor)

2. Časování instrukcí na mikrořadičích AVR a rozdělení instrukcí do kategorií

Na konci předchozí kapitoly jsme se letmo zmínili o tom, že instrukce, tj. instrukční kódy i operandy, jsou v naprosté většině případů načítány v jednom taktu. Ve skutečnosti dochází k překrývání provádění instrukcí – zatímco je v jednom strojovém taktu načítána další instrukce z paměti programu, je současně spouštěna operace definovaná v instrukci načtené v předchozím strojovém taktu. Toto překrývání je dalším znakem Harvardské architektury, protože díky oddělení paměti programu a paměti dat je zaručeno, že nedojde ke kolizím na adresové a datové sběrnici. U většiny instrukcí je vlastní operace rozložena na tři podoperace – načtení operandu či dvou operandů do záchytných registrů ALU, provedení vybrané ALU operace (součet, bitový posuv, inkrementace, bitový test …) a konečně zápis výsledku operace zpět do některého pracovního registru. Všechny tři podoperace jsou provedeny v jediném strojovém taktu (samozřejmě však existují instrukce, u nichž je časování a vlastně i způsob načítání jejich instrukčního kódu složitější).

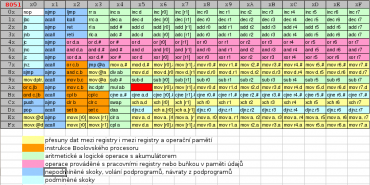

Obrázek 3: Instrukční sada osmibitového mikrořadiče MCS-51.

(Zdroj: Gnumeric + cca hodina práce :-)

Instrukce osmibitových mikrořadičů AVR lze rozdělit podle mnoha kritérií (typ instrukce, formát instrukčního kódu, typ použitého adresního režimu atd.). My si nejdříve popíšeme některé nejtypičtější formáty instrukcí a posléze se budeme zabývat vybranou skupinou instrukcí, které mohou být některou svou vlastností zajímavé a odlišné od jiných platforem. Rozdělení instrukcí podle formátu instrukčního slova a formátu operandů je poměrně snadné. Instrukce totiž můžeme rozdělit na skupinu instrukcí operujících s jediným pracovním registrem, instrukce operující s dvojicí pracovních registrů, instrukce operující s jedním pracovním registrem a jedním registrem speciálních funkcí ležícím v I/O oblasti, instrukce obsahující přímou šestnáctibitovou adresu, popř. adresu určenou některým z adresních registrů X, Y či Z a nakonec instrukce skoků, které mohou být v závislosti na typu instrukce prováděny buď na absolutní nebo relativní adresu.

Obrázek 4: Bloková struktura osmibitových mikrořadičů AVR.

3. Instrukce provádějící operaci s jedním nebo dvěma pracovními registry

Některé aritmetické, logické a bitové instrukce provádějí operaci pouze s jediným pracovním registrem. Jedná se například o instrukce CLR (vynulování všech bitů pracovního registru), COM (jedničkový doplněk pracovního registru), NEG (dvojkový doplněk pracovního registru), INC (zvýšení hodnoty pracovního registru o jedničku), DEC (snížení hodnoty pracovního registru o jedničku), SER (nastavení všech bitů na jedničku), LSL (logický posuv doleva), LSR (logický posuv doprava), ROL (rotace doleva), ROR (rotace doprava), ASR (aritmetický posuv doprava) a SWAP (prohození horní a spodní čtveřice bitů). V operačních kódech těchto instrukcí je zapotřebí určit pouze index jednoho pracovního registru, který lze zakódovat do pěti bitů – ostatních jedenáct bitů obsahuje instrukční kód. Ovšem některé výše zmíněné instrukce ve skutečnosti používají stejné kódování jako instrukce se dvěma operandy – v tomto případě je ovšem index zdrojového a cílového registru shodný.

Obrázek 5: Instrukce pracující s jediným operandem mají v pěti bitech svého šestnáctibitového instrukčního slova uloženo číslo registru, který je použit jako zdrojový a současně i jako cílový operand.

Tím se dostáváme k poměrně velké skupině aritmetických a logických instrukcí se dvěma operandy. U architektury AVR je použit takzvaný dvouadresový kód, podobně jako u naprosté většiny v současnosti používaných mikroprocesorů a mikrořadičů. Toto označení znamená, že u instrukcí se dvěma operandy je jeden z těchto operandů použitý jak pro poskytnutí vstupních dat, tak i pro uložení výsledku operace. Z více než šedesátileté praxe vývoje instrukčních sad programovatelných počítačů se totiž ukázalo, že dvouadresový kód je pro většinu účelů dostatečně flexibilní, ale naproti tomu nejsou instrukční slova zbytečně dlouhá tak, jako by tomu muselo být u kódu tříadresového, kde se kromě obou vstupních operandů explicitně specifikuje i to, kam se má uložit výsledek operace (například by se jednalo o instrukci ADD r0, r1, r20, zatímco u dvouadresového kódu lze pouze zapsat ADD r0, r1). V případě mikrořadičů AVR je u instrukcí pracujících se dvěma operandy první operand (pracovní registr) určen pěti bity a druhý operand taktéž pěti bity. Zbylých šest bitů instrukčního slova je použito pro uložení instrukčního kódu.

Obrázek 6: V šestnáctibitovém instrukčním slovu je dostatek místa na uložení jak čísla zdrojového registru, tak i čísla registru cílového. Z tohoto hlediska tedy mají všechny pracovní registry funkci stejnou jako akumulátor.

4. Podmíněné skoky

V předchozí kapitole jsme popisem instrukcí pracujících s jedním nebo dvěma registry pokryli poměrně značnou část instrukčního kódu mikrořadičů AVR – to je ostatně typické i pro další architektury typu RISC, u nichž většina aritmetických a logických instrukcí může operovat pouze s pracovními registry, zatímco složitější adresní režimy jsou vyhrazeny většinou (téměř výhradně) na instrukce čtení a zápisu dat z/do pracovních registrů (LD, ST). Nicméně další důležitou částí instrukční sady jsou podmíněné skoky. Jedná se o instrukce pracující na základě aktuálních hodnot podmínkových bitů uložených ve stavovém registru popsaném minule – zde se tedy naopak architektura AVR dosti podstatným způsobem odlišuje například od čistě RISCové architektury MIPS, kde se jejím tvůrcům podařilo vyhnout se nutnosti použití stavového registru, což sice některé programové konstrukce poněkud komplikuje, na druhou stranu je však z procesoru odstraněna další stavová informace komplikující například přepínání vláken, reakci na přerušení, vracení předpřipravených výsledků operací při špatné predikci skoku a/nebo přepínání výpočtů mezi několika ALU.

Obrázek 7: Formát instrukce BRBS. Povšimněte si, že v instrukčním slovu je uložena jak relativní adresa skoku, tak i tři bity pro index testovaného bitu stavového registru.

Nicméně se vraťme k podmíněným skokům u osmibitových mikrořadičů AVR. Tyto skoky obsahují přímo ve svém instrukčním slovu sedmibitovou konstantu umožňující provést relativní skok na adresu PC-64 až PC+63, samozřejmě s tím dodatkem, že delší skoky (v rámci celého adresního prostoru paměti programu) lze zapsat dvojicí instrukcí: podmíněného skoku s opačnou podmínkou následovaného nepodmíněným „dlouhým“ skokem. Všechny typy podmíněných skoků jsou vypsány v tabulce uvedené v následující kapitole. Povšimněte si, že podmíněné skoky jsou rozděleny do několika skupin: skoky podporující testování čísel bez znaménka, skoky podporující testování čísel se znaménkem (v oblasti osmibitovým mikrořadičů ne zcela obvyklé!), skoky pro zpracování dalších příznaků (interrupt flag…) a konečně skoky využívané při práci s jediným příznakovým bitem, který je možné meziuložit do bitu T stavového registru.

Obrázek 8: Formát instrukce BRBC je až na obsah jediného bitu shodný s formátem instrukce BRBS.

5. Tabulka podmíněných skoků

V následující tabulce jsou vypsány všechny podmíněné skoky podporované osmibitovými mikrořadiči AVR. Povšimněte si zejména jedné zajímavosti, která spočívá v tom, že všechny podmíněné skoky jsou ve skutečnosti reprezentovány pouze dvojicí instrukcí BRBC s,k (proveď skok, pokud je bit s stavového registru nulový) a BRBS s,k (proveď skok, pokud je bit s stavového registru jedničkový). Tato vlastnost instrukční sady AVR je umožněna tím, že přímo ve stavovém registru je umístěn i v podstatě nadbytečný příznak S (signum flag), který je po každé aritmetické a logické operaci vypočten ze dvou dalších příznaků N (negative flag) a V (two's complement overflow flag) následovně: S = N xor V. Díky existenci tohoto příznaku vyhodnocovaného přímo aritmeticko-logickou jednotkou bylo možné zjednodušit logiku řadiče při provádění podmíněných skoků:

| Instrukce | Ekvivalent | Typ | Popis |

|---|---|---|---|

| BRBC s,k | × | obecný skok | Branch if Status Flag s Cleared |

| BRBS s,k | × | obecný skok | Branch if Status Flag s Set |

| BREQ k | BRBS 1,k | bez/se znaménkem | Branch if Equal (Z = 1) |

| BRNE k | BRBC 1,k | bez/se znaménkem | Branch if Not Equal (Z = 0) |

| BRCS k | BRBS 0,k | bez znaménka | Branch if Carry Set if (C = 1) |

| BRCC k | BRBC 0,k | bez znaménka | Branch if Carry Cleared if (C = 0) |

| BRSH k | BRBC 0,k | bez znaménka | Branch if Same or Higher if (C = 0) |

| BRLO k | BRBS 0,k | bez znaménka | Branch if Lower if (C = 1) |

| BRGE k | BRBC 4,k | se znaménkem | Branch if Greater or Equal, Signed if (N xor V= 0) |

| BRLT k | BRBS 4,k | se znaménkem | Branch if Less Than, Signed if (N xor V= 1) |

| BRMI k | BRBS 2,k | se znaménkem | Branch if Minus if (N = 1) |

| BRPL k | BRBC 2,k | se znaménkem | Branch if Plus if (N = 0) |

| BRVS k | BRBS 3,k | se znaménkem | Branch if Overflow Flag is Set if (V = 1) |

| BRVC k | BRBC 3,k | se znaménkem | Branch if Overflow Flag is Cleared if (V = 0) |

| BRHS k | BRBS 5,k | BCD aritmetika | Branch if Half Carry Flag Set if (H = 1) |

| BRHC k | BRBC 5,k | BCD aritmetika | Branch if Half Carry Flag Cleared if (H = 0) |

| BRTS k | BRBS 6,k | bitový test | Branch if T Flag Set if (T = 1) |

| BRTC k | BRBC 6,k | bitový test | Branch if T Flag Cleared if (T = 0) |

| BRIE k | BRBS 7,k | bitový test | Branch if Interrupt Enabled if (I = 1) |

| BRID k | BRBC 7,k | bitový test | Branch if Interrupt Disabled if (I = 0) |

Obrázek 9: Překrývání načítání a provádění instrukcí u osmibitových mikrořadičů AVR.

6. Podmíněné instrukce typu SKIP

Zajímavým a užitečným doplňkem k podmíněným skokům je pětice instrukcí typu SKIP. Jedná se o instrukce, které po splnění nějaké podmínky přeskočí následující instrukci (jde tedy o podobné typy instrukcí, s jakými jsme se již setkali při popisu osmibitových mikrořadičů PIC). V praxi to znamená, že pokud podmínka není splněna, zvýší se čítač instrukcí PC o jedničku (bude ukazovat na následující instrukci), zatímco pokud je podmínka splněna, je obsah PC zvýšen o dvojku nebo o trojku, v závislosti na tom, zda má instrukce následující za instrukcí typu SKIP délku jednoho nebo dvou slov (již minule jsme si řekli, že PC adresuje instrukce po dvoubajtových slovech, nikoli po jednotlivých bajtech). Důvod pro existenci instrukcí typu SKIP je v podstatě velmi jednoduchý – kvůli tomu, že v instrukčním kódu těchto instrukcí je uveden i index pracovního registru (popř. registru z I/O prostoru) a taktéž index testovaného bitu 0–7 (nebo index druhého pracovního registru), není zde již místo pro uložení relativní adresy skoku a tvůrci instrukční sady mikrořadičů AVR nechtěli, aby se zbytečně zvyšoval počet 32bitových instrukcí.

Obrázek 10: Osmibitový mikrořadič AVR ATtiny-4 s šestipinovém pouzdru.

V následující tabulce je vypsáno všech pět podporovaných instrukcí typu SKIP:

| Jméno instrukce | Operand číslo 1 | Operand číslo 2 | Popis instrukce |

|---|---|---|---|

| SBRC | pracovní registr 0–31 | index bitu 0–7 | skip pokud je daný bit pracovního registru nulový |

| SBRS | pracovní registr 0–31 | index bitu 0–7 | skip pokud je daný bit pracovního registru nastaven na jedničku |

| SBIC | I/O registr 0–31 | index bitu 0–7 | skip pokud je daný bit I/O registru nulový |

| SBIS | I/O registr 0–31 | index bitu 0–7 | skip pokud je daný bit I/O registru nastaven na jedničku |

| CPSE | pracovní registr 0–31 | pracovní registru 0–31 | skip pokud je obsah obou registrů shodný |

Obrázek 11: Osmibitový mikrořadič AVR ATtiny-4 s osmipinovém pouzdru, kde je ovšem ve skutečnosti zapojeno pouze šest pinů, podobně jako na předchozím obrázku.

7. Práce s jednobitovými hodnotami

V předchozí kapitole jsme si popsali instrukce typu SKIP, které jsou zároveň instrukcemi pracujícími s jednotlivými bity pracovních registrů nebo I/O registrů. Vzhledem k tomu, že osmibitové mikrořadiče AVR, stejně jako vlastně i všechny další osmibitové mikrořadiče, obsahují v I/O oblasti mnoho registrů speciálních funkcí, s nimiž se efektivně operuje pouze na bitové úrovni, jsou bitové operace nedílnou a velmi užitečnou součástí instrukční sady mikrořadičů AVR. Představme si například, že chceme blikat LED připojenou na jeden z pinů portu B. Je samozřejmě možné pomocí bitových masek nastavovat a nulovat bit odpovídající vybranému pinu, ovšem mnohem jednodušší je použít bitovou operaci pro nastavení pinu na nulu či jedničku (při zápisu do I/O registru PORTB), popř. negovat původní logickou hodnotu na pinu zápisem jedničky do příslušného bitu I/O registru PINB. Některé další bitové instrukce navíc slouží pro manipulaci s příznakem T uloženým ve stavovém registru. Připomeňme si, že obsah tohoto bitu lze použít v podmíněných skocích BRTS (skok pokud je T jedničkový) a BRTC (skok pokud je T nulový).

Obrázek 12: Struktura jednoho vstupně-výstupního pinu mikrořadiče AVR. Povšimněte si možnosti připojit na pin interní pull-up rezistor.

Bitově orientované instrukce, včetně instrukcí podmíněného skoku zmíněných v předchozích kapitolách, jsou vypsány v následující tabulce:

| Jméno instrukce | Typ instrukce | Popis |

|---|---|---|

| SET | nastavení bitu T | nastavení bitu T na jedničku |

| CLT | nastavení bitu T | vynulování bitu T |

| BLD Rd, b | práce s bitem T | nastavení bitu bbb pracovního registru Rd na hodnotu určenou bitem T |

| BST Rd, b | práce s bitem T | nastavení bitu T z bitu bbb pracovního registru Rd |

| BRTS k | podmíněný skok | skok pokud je bit T jedničkový |

| BRTC k | podmíněný skok | skok pokud je bit T nulový |

| SBI A, b | I/O operace | nastavení bitu b v registru speciálních funkcí ležícího v I/O oblasti |

| CBI A, b | I/O operace | vynulování bitu b v registru speciálních funkcí ležícího v I/O oblasti |

Obrázek 13: Automatická pre-dekrementace adresy při použití adresních registrů X, Y a Z.

8. Adresování používané u instrukcí typu LD (Load) a ST (Store)

V předchozí části seriálu o architekturách počítačů jsme si mj. řekli i to, jakým způsobem je poslední šestice osmibitových pracovních registrů používána ve formě trojice šestnáctibitových adresních registrů X, Y a Z. Tyto adresní registry jsou využívány především v instrukcích typu LD (Load) a ST (Store). Obsah libovolného adresního registru může být použit pro nepřímé adresování operandu uloženého v paměti dat, popř. se také může provést post-inkrementace nebo pre-dekrementace obsahu adresního registru (vhodné například pro procházení polem). Navíc je při použití registrů Y a Z možné k obsahu registru přičíst šestibitový offset uložený přímo v instrukčním kódu. Registr Z má ještě jeden speciální význam – lze ho použít při adresování dat uložených v paměti programu, tj. mohou zde být uloženy například různé kódovací tabulky atd. Instrukce LDS se od ostatních instrukcí odlišuje v tom, že za instrukčním kódem je umístěna šestnáctibitová přímá adresa – jedná se tedy o jednu z několika málo instrukcí o délce 32 bitů.

Obrázek 14: Automatická post-inkrementace adresy při použití adresních registrů X, Y a Z.

V následující tabulce jsou vypsány různé varianty instrukce LD (Load) s tím, že u instrukcí ST (Store) jsou možnosti podobné, i když například instrukce LDI nemá z pochopitelného důvodu svůj ekvivalent:

| Instrukce | Délka | Popis |

|---|---|---|

| LDI Rd, k | 16b | načtení konstanty do pracovního registru Rd |

| LDS Rd, k | 32b | načtení hodnoty z adresy zadané šestnáctibitovou konstantou |

| LD Rd, X | 16b | načtení bajtu z adresy (X) – nepřímé adresování |

| LD Rd, X+ | 16b | načtení bajtu z adresy (X), inkrementace adresního registru X |

| LD Rd, -X | 16b | dekrementace X, načtení bajtu z adresy (X) |

| LD Rd, Y | 16b | načtení bajtu z adresy (Y) |

| LD Rd, Y+ | 16b | načtení bajtu z adresy (Y), inkrementace adresního registru Y |

| LD Rd, -Y | 16b | dekrementace Y, načtení bajtu z adresy (Y) |

| LD Rd, Y+q | 16b | načtení bajtu z adresy (Y+q), kde q je šestibitový offset |

| LD Rd, Z | 16b | načtení bajtu z adresy (Z) |

| LD Rd, Z+ | 16b | načtení bajtu z adresy (Z), inkrementace adresního registru Z |

| LD Rd, -Z | 16b | dekrementace Z, načtení bajtu z adresy (Z) |

| LD Rd, Z+q | 16b | načtení bajtu z adresy (Z+q), kde q je šestibitový offset |

| LPM Z | 16b | načtení bajtu z paměti programu adresované (Z) do registru R0 (speciální formát pouze pro tento registr) |

| LPM Rd, Z | 16b | načtení bajtu z paměti programu adresované (Z) do registru Rd |

| LPM Rd, Z+ | 16b | načtení bajtu z paměti programu adresované (Z) do registru Rd, inkrementace Z |

Obrázek 15: Další podporovaný způsob adresování, kdy se k bázové adrese uložené v některém z adresních registrů Y nebo Z přičítá šestibitový offset.

9. Odkazy na Internetu

- AVRFreaks Wiki

http://www.avrfreaks.net/wiki/index.php/Main_Page - Atmel AVR 8– and 32-bit

http://www.atmel.com/products/avr/ - tinyAVR

http://www.atmel.com/dyn/products/devices.asp?category_id=163&family_id=607&subfamily_id=791 - AT-Mini

http://www.mikroe.com/eng/products/view/649/at-mini-board/ - Arduino

http://www.arduino.cc/ - AVR Microcontroller

http://www.engineersgarage.com/articles/avr-microcontroller - Atmel AVR – Wikipedia

http://en.wikipedia.org/wiki/Atmel_AVR - AVR instruction set

http://avr.hw.cz/architektura/instukce.html - Porovnání jednotlivých procesorů AVR

http://avr.hw.cz/architektura/porovnani.html - 68HC11 Instruction Set

http://www.cs.uaf.edu/2007/fall/cs441/proj1notes/sawyer/inst.html - 68HC11 OpCode Map

http://home.earthlink.net/~tdickens/68hc11/68hc11_opcode_map.html - A Simple Robot Using the 68HC11 Processor

http://home.earthlink.net/~tdickens/68hc11/trp2/trp2.html - 68HC11 C-Compiler (Imagecraft)

http://microcontrollershop.com/product_info.php?products_id=188 - GNU Development Chain for 68HC11&68HC12

http://www.gnu.org/software/m68hc11/ - GNU C for 68HC11 – documentation

http://www.gnu.org/software/m68hc11/m68hc11_doc.html - The P-Brain tm Microcontroller Kit

http://www.futurebots.com/brain.htm - Wikipedia: Motorola 68HC05

http://en.wikipedia.org/wiki/Motorola_68HC05 - Wikipedia: Freescale 68HC08

http://en.wikipedia.org/wiki/68HC08 - Wikipedia: Freescale 68HC11

http://en.wikipedia.org/wiki/68HC11 - Wikipedia: Freescale 68HC12

http://en.wikipedia.org/wiki/Freescale_68HC12 - HC05 Processor Families

http://www.freescale.com/webapp/sps/site/overview.jsp?nodeId=01624684498633 - HC08 Processor Families

http://www.freescale.com/webapp/sps/site/overview.jsp?nodeId=01624684497663 - Digital Core Design 68HC08 – HDL IP Core

http://www.dcd.pl/acore.php?idcore=82 - Freescale 68HC11

http://www.freescale.com/webapp/sps/site/taxonomy.jsp?nodeId=01624684498635 - Lifecycle of a CPU:

http://www.cpushack.net/life-cycle-of-cpu.html - Most wanted CPU of the world:

http://www.cpu-galaxy.at/CPU/Intel%20CPU/3002–8008/4004%20Grey.jpg - Wikipedia: 6502:

http://en.wikipedia.org/wiki/6502 - The Western Design Center, Inc.:

http://www.westerndesigncenter.com/ - Apple II History Home:

http://apple2history.org/ - www.6502.org:

http://www.6502.org/ - Stránky firmy Microchip Technology

http://www.microchip.com/ - Výběr z různých modelů (osmibitových) mikrořadičů PIC

http://www.microchip.com/stellent/idcplg?IdcService=SS_GET_PAGE&nodeId=2661 - Řada (rodina) osmibitových mikrořadičů PIC 10

http://www.microchip.com/ParamChartSearch/chart.aspx?branchID=1009&mid=10&lang=en&pageId=74 - Řada (rodina) osmibitových mikrořadičů PIC 12

http://www.microchip.com/ParamChartSearch/chart.aspx?branchID=1001&mid=10&lang=en&pageId=74 - Řada (rodina) osmibitových mikrořadičů PIC 14

http://www.microchip.com/ParamChartSearch/chart.aspx?branchID=1008&mid=10&lang=en&pageId=74 - Řada (rodina) osmibitových mikrořadičů PIC 16

http://www.microchip.com/ParamChartSearch/chart.aspx?branchID=1002&mid=10&lang=en&pageId=74 - Další výběr z různých modelů mikrořadičů PIC

http://www.microchip.com/maps/microcontroller.aspx - PIC microcontroller (Wikipedia EN)

http://en.wikipedia.org/wiki/PIC_microcontroller - Mikrokontrolér PIC (Wikipedia CZ)

http://cs.wikipedia.org/wiki/Mikrokontrolér_PIC - FLASHFORTH for the PIC18F and the dsPIC30F

http://flashforth.sourceforge.net/ - FlashForth

http://www.sourceforge.net/projects/flashforth - Free Pic software tools

http://softwarepic.50webs.com/freesoft.html - What is Amicus?

http://www.picbasic.org/proton_lite.php - Amicus FAQ

http://www.myamicus.co.uk/faq.php?s=2e8d12e7f4c23e775776f4916876354b& - Microcontrollers development tools

http://www.gnupic.dds.nl/ - gpsim (Wikipedia EN)

http://en.wikipedia.org/wiki/Gpsim - gpsim home page

http://gpsim.sourceforge.net/gpsim.html - The FreeRTOS Project

http://www.freertos.org/ - FreeRTOS (Wikipedia)

http://en.wikipedia.org/wiki/FreeRTOS - Serial EEPROM (93C46 / 93CS46) Routines

http://www.pjrc.com/tech/8051/serial-eeprom.html - Great Microprocessors of the Past and Present (V 13.4.0)

http://jbayko.sasktelwebsite.net/cpu.html - SPI interface tutorial

http://www.best-microcontroller-projects.com/spi-interface.html - Serial Peripheral Interface Bus

http://en.wikipedia.org/wiki/Serial_Peripheral_Interface_Bus - EUSB to SPI bus Kit

http://www.eidusa.com/Electronics_Kits_EUSB_To_SPI_BUS.htm - SPI Block Guide V03.06, Freescale Semiconductor

http://www.freescale.com/files/microcontrollers/doc/ref_manual/S12SPIV3.pdf - What is SPI?

http://www.fpga4fun.com/SPI1.html - SPI – A simple implementation

http://www.fpga4fun.com/SPI2.html - Bit-banging

http://en.wikipedia.org/wiki/Bit-banging - Joint Test Action Group

http://en.wikipedia.org/wiki/JTAG - I2C

http://en.wikipedia.org/wiki/I2C - Seriál o programovacím jazyce Forth:

seriál o programovacím jazyce Forth - Display Data Channel

http://en.wikipedia.org/wiki/Display_Data_Channel - I2 Background

http://www.microport.tw/blognew.php?blog_no=7#theory - PIC16F87X, 28/40-pin 8-Bit CMOS FLASH Microcontrollers

Microchip Technology Inc.

http://www.microchip.com