Obsah

1. Digitální signálové procesory řady Motorola 56000

2. Architektura DSP Motorola 56000

5. Šířka zpracovávaných operandů

9. Aritmeticko-logická jednotka

10. Použití DSP řady Motorola 56000

11. Doplněk na závěr – řada 56000 v porovnání s TMS320C10

1. Digitální signálové procesory řady Motorola 56000

V předchozích sedmi částech seriálu o architekturách počítačů jsme se seznámili s některými milníky společnosti Texas Instruments ve vývoji digitálních signálových procesorů. Připomeňme si, že se jednalo o řadu TMS320×x, která se postupně vyvinula od poměrně jednoduchého čipu TMS32010 až k současným výkonným čipům OMAP a DaVinci. Dnes se ve stručnosti seznámíme s dalším čipem, který hrál velmi důležitou roli ve vývoji digitálních signálových procesorů. Jedná se o procesor nazvaný Motorola 56000 (neboli zkráceně 56k), který patří do druhé generace digitálních signálových procesorů. Tato generace je charakteristická použitím architektury s větším množstvím datových sběrnic, nabídkou speciálních typů adresování použitelných například pro výpočet FFT či různými instrukcemi pro optimalizaci programových smyček (DSP třetí generace šly ještě dále a nabídly specializované koprocesory pro FFT či násobení matic, ve čtvrté generaci se pak používá architektura VLIW, SIMD, popř. superskalární architektura). DSP druhé generace se již většinou programovaly v jazyku C s tím, že pro výpočty typické pro zpracování signálů byly vytvořeny optimalizované knihovny.

Všechny čipy ze základní série Motorola 56000 obsahují prakticky totožné jádro, ovšem liší se například kapacitami pamětí programu a dat, konfigurací periferních zařízení a taktéž tím, zda obsahují či naopak neobsahují takzvaný Port A, který zprostředkovává přístup k externím pamětem (u jednodušších čipů by byl tento port sestavený ze 16bitové adresové sběrnice, 24bitové datové sběrnice a deseti řídicích signálů příliš velkým luxusem). Ovšem kromě základní řady 56000 byly společností Motorola navrženy i další podobně koncipované digitální signálové procesory, které se od sebe odlišují šířkou zpracovávaných operandů i jejich typickým použitím:

| Označení | Typ čipu |

|---|---|

| DSP560XX | původní série označovaná souhrnně 56000 či 56k, 24bitové zdrojové operandy, 56bitové mezivýsledky |

| DSP563XX | hybridní 16/24bitový DSP |

| DSP566XX | menší DSP se šestnáctibitovými vstupními operandy |

| DSP567XX | takzvaný Digital Signal Controller, kombinace MCU a DSP |

| DSP568XX | takzvaný Digital Signal Controller, kombinace MCU a DSP |

| DSP96000 | nová řada zpětně kompatibilní s řadou 56000, ovšem rozšířená o FP operace (tato řada prozatím obsahuje jen čip 96002) |

Obrázek 1: Osobní počítač Atari Falcon030, který je založen na kombinaci tří procesorů a koprocesorů – hlavního CPU Motorola 68030, digitálního signálového procesoru Motorola 56001 a volitelného matematického koprocesoru Motorola 68881/2.

2. Architektura DSP Motorola 56000

Digitální signálové procesory Motorola řady 56000 mají poměrně zajímavou strukturu, která byla navržena především s ohledem na zpracování zvukových signálů v kvalitě, která odpovídala možnostem tehdejší techniky (reálná přesnost A/D převodníků apod.). Interně je 56000 založena na modifikované Harvardské architektuře, což znamená, že paměť určená pro uložení programového kódu a konstant je oddělena od paměti určené pro data. Ve skutečnosti však šli návrháři Motoroly 56000 v rozdělování paměti na více samostatných bloků ještě dále, protože se používají celkem tři různé oblasti: paměť pro uložení programu označovaná P-space, první segment paměti pro data označovaný X-space/X data a druhý segment paměti pro data označovaný Y-space/Y data. Rozdělení datové paměti na dva segmenty dává pro mnoho operací smysl, jelikož v prvním segmentu mohou být například uloženy zdrojové digitalizované signály a v oblasti druhé výsledek jejich zpracování.

Obrázek 2: Blokové schéma digitálního signálového procesoru Motorola 56000.

Na obrázku číslo 2 je zobrazeno blokové schéma jednoho konkrétního čipu ze série Motorola 56000. Základní jádro je u všech digitálních signálových procesorů z této série shodné (šedě podbarvená část), ovšem horní část schématu se může lišit. Týká se to především kapacit pamětí programu a obou segmentů paměti dat. Povšimněte si, že v tomto konkrétním čipu jsou v datových pamětech uloženy i tabulky konstant, zde konkrétně převodní tabulky pro funkce algoritmu A-law a µ-law (vlastně se nejedná o nijak komplikované algoritmy, ale o dvojici funkcí) a taktéž o tabulku hodnot funkce sinus (ve formátu s pevnou řádovou čárkou, resp. ještě přesněji řečeno ve formátu, kde je desetinná čárka umístěna ihned za znaménkový bit), což je pro mnoho algoritmů velmi užitečné. Nezávisle na tom, jak velkou mají jednotlivé paměťové bloky kapacitu je šířka slov vždy 24 bitů.

3. Datové sběrnice

Některé čipy z řady DSP 56000 mají vyvedenou jednu externí 24 bitovou datovou sběrnici (ta je součástí Portu A neboli Memory Expansion Portu zmíněného již v úvodní kapitole) umožňující připojení externích pamětí, dalších DSP či periferních zařízení. Interně se na čipu přenáší data po čtyřech nezávislých datových sběrnicích, přičemž každá sběrnice má šířku 24 bitů (viz též pátou kapitolu). V následující tabulce jsou uvedeny základní charakteristiky těchto sběrnic:

| Zkratka | Význam | Popis |

|---|---|---|

| XDB | X data bus | přenos mezi ALU, pracovními registry a prvním segmentem paměti dat |

| YDB | Y data bus | přenos mezi ALU, pracovními registry a druhým segmentem paměti dat |

| PDB | Program data bus | přenos kódů instrukcí, generování adres |

| GDB | Global data bus | ostatní přenosy, I/O, komunikace apod. |

Operandy vstupující do aritmeticko-logické jednotky mají většinou šířku 24 bitů, ovšem výsledek operace multiply-accumulate může být 56 bitový. V tomto případě je část výsledku (konkrétně 48 bitů vystupujících ze shifteru) přenášena po obou sběrnicích XDB+YDB současně.

4. Adresové sběrnice

Adresy instrukcí či zpracovávaných dat se přenáší po třech interních adresových sběrnicích. Tyto sběrnice mají na původních čipech šířku jen šestnáct bitů, z čehož vyplývají i omezení na maximální adresovatelný rozsah (adresuje se po 24bitových slovech, nikoli po bajtech, takže maximální kapacita datových RAM je 64K × 3 ×2 = 384 KB):

| Zkratka | Popis |

|---|---|

| XAB | adresa pro operand přenášený po sběrnici XDB |

| YAB | adresa pro operand přenášený po sběrnici YDB |

| PAB | adresa další instrukce |

Opět platí, že některé digitální signálové procesory řady 56000 mají vyvedenou jednu externí adresovou sběrnici, která společně s generátorem řídicích signálů a externí datovou sběrnicí tvoří již zmíněný Port A (Memory Expansion Port).

5. Šířka zpracovávaných operandů

Digitální signálové procesory Motorola 56000 zpracovávají vstupní operandy o šířce 24 bitů, což se sice na první pohled může zdát poněkud zvláštní (u běžných mikroprocesorů se většinou používají šířky 8, 16, 32 a 64 bitů, ostatně to bylo dodrženo i u naprosté většiny již popsaných DSP řady TMS320C10), ovšem pro zpracování zvukových signálů byla čtyřiadvacetibitová šířka více než vhodná, protože koresponduje s možnostmi v té době používaných D/A a A/D převodníků, které byly většinou dvacetibitové. Použitím šestnáctibitové datové šířky by bylo možné pracovat se signály s dynamickým rozsahem „pouze“ 96 dB (20×log 216), zatímco 24bitové vzorky mají dynamický rozsah 144 dB (20×log 224). Při zpracování 32bitových slov by se naopak musela používat zbytečně složitá aritmeticko-logická jednotka, která by zvyšovala cenu celého procesoru (navíc je násobení i pomalejší nebo by vyžadovalo příliš velkou plochu čipu – opět viz úspěšná minimalisticky pojatá TMS320C10 s násobičkou 16b×16b) a navíc by se při ukládání vzorků plýtvalo s operační pamětí. Mimochodem: Motorola 56000 při výpočtech používá aritmetiku s pevnou řádovou čárkou (tečkou), která se v materiálech nazývá fractional a popíšeme i ji v dalších kapitolách.

Obrázek 2: Karta pro zpracování audio signálů využívající DSP Motorola 56000.

6. Sada pracovních registrů

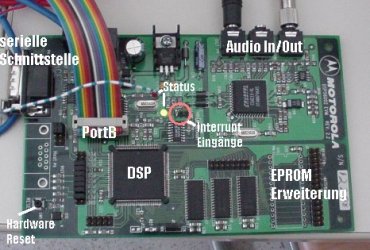

Digitální signálové procesory Motorola 56000 obsahují celkem čtyři pracovní registry a dva akumulátory, které je taktéž možné považovat za pracovní registry, i když akumulátory u DSP skutečně pracují jako akumulátory, na rozdíl od běžných CPU. Čtyři pracovní registry se jmenují X0, X1, Y0 a Y1, přičemž každý má šířku 24 bitů. V některých případech je možné vždy dvojici těchto registrů vzájemně spojit a vytvořit tak 48bitové registrové páry X1:X0 a Y1:Y0. Hlavní funkcí pracovních registrů je poskytovat data aritmeticko-logické jednotce, proto jsou registry připojeny mezi datové sběrnice XDB a YDB (tok dat může v tomto případě probíhat oběma směry) a násobičkou (tok dat probíhá jednosměrně registr→násobička). Tento koncept je odlišný od konceptu, který známe z řady TMS320.

Obrázek 3: Schéma jádra digitálního signálového procesoru Motorola 56000. Čtveřice pracovních registrů je zobrazena v horní části a je obarvena modře. Povšimněte si, jak jsou registry propojeny se sběrnicemi (obousměrně) i s násobičkou (jednosměrně). Čísla značí bitovou šířku dat.

Obrázek 4: Pro porovnání – interní struktura nejdůležitější části DSP TMS32010, v níž se provádí všechny výpočty.

7. Akumulátory

Dvojice akumulátorů je pojmenována jednoduše A a B. Tyto akumulátory jsou připojeny na výstup z aritmeticko-logické jednotky (současně jsou připojeny na vstup ALU i na obě datové sběrnice XDB a YDB. Na rozdíl od pracovních registrů s šířkou 24 bitů mají akumulátory šířku 56 bitů. Proč tomu tak je? Hlavní operací, kterou DSP provádí, je násobení dvou operandů, přičemž v tomto případě akceptuje násobička dvojici operandů s šířkou 24 bitů. Výsledkem násobení je 48bitová hodnota, která je přičtena k akumulátoru s šířkou 56 bitů. Programátor má tedy k dipozici celých osm bitů navíc, takže se nemusí bát, že například při implementaci nějakého filtru dojde k přetečení mezivýsledků – tyto starosti bude muset řešit až při ukládání výsledků z akumulátorů zpět do paměti, k čemuž mj. slouží blok nazvaný shifter/limiter, jehož úkolem je získat z hodnoty akumulátoru použitelný 24bitový či 48bitový výsledek.

Poznámka: interně jsou akumulátory rozděleny na tři části, takže například akumulátor A je tvořen trojicí 24bitových registrů pojmenovaných A2, A1 a A0, přičemž v registru A2 má význam jen spodních osm bitů.

Obrázek 5: Akumulátory (zvýrazněné modrou barvou) jsou připojeny k výstupu z aritmeticko-logické jednotky. Dále je možné do akumulátorů zapisovat data přímo z datových sběrnic. Z akumulátorů si operandy čte ALU, a to jak přímo, tak i přes shifter. Zápis zpět do paměti se provádí vždy přes shifter/limiter, který zajistí konverzi dat.

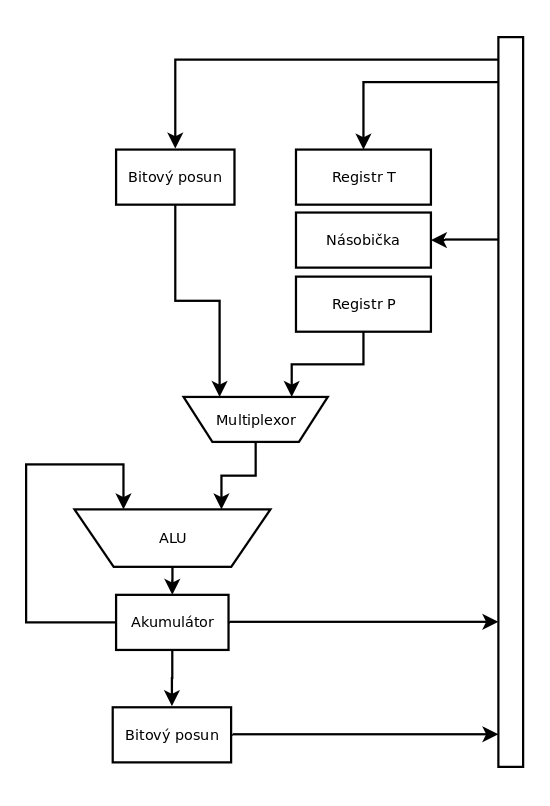

8. Násobička

Ústředním prvkem prakticky všech digitálních signálových procesorů první i druhé generace je násobička. U DSP Motorola 56000 je násobička napevno umístěna mezi pracovní registry a aritmeticko logickou jednotku – vstupem do násobičky jsou tedy vždy pouze obsahy dvou vybraných pracovních registrů, tj. X0, X1, Y0 a/nebo Y1 (ty mají šířku 24 bitů, jak již víme z předchozího textu). Násobička oba 24bitové operandy vynásobí a pošle 48bitový výsledek do aritmeticko-logické jednotky, která dokončí operaci typu MAC, popř. „přičte nulu“ pokud je pouze vyžadováno násobeni.

U této architektury digitálních signálových procesorů je v souvislosti s násobičkou nutné poznamenat, že se používá formát čísel nazvaný fractional. Nejedná se vlastně o nic jiného, než o jednu z možností reprezentace hodnot v systému pevné řádové čárky (fixed point), ovšem tak, že čárka není ve slově umístěna libovolně, ale je vložena ihned za znaménkový bit (používá se běžný dvojkový doplněk). To znamená, že 24bitová slova vstupující do násobičky mají tento formát (s – znaménkový bit, čárka – binární čárka):

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+ |s , | +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

Minimální reprezentovatelná hodnota je rovna přesně –1, což odpovídá 24bitovému slovu s bitovým vzorkem 0×80000:

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+ |-1, 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0| +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

Maximální hodnota je rovna 1–2-23=.99999988 (tedy „skoro jedna“) a odpovídá 24bitovému slovu s bitovým vzorkem 0×7fffff:

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+ | 0, 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1| +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

Hodnotu 0,5 (1/2) lze zapsat takto:

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+ | 0, 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0| +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

Poznámka: pro aritmetické a logické operace není mezi celočíselnými hodnotami a hodnotami „fractional“ žádný podstatný rozdíl. Ten se projevuje pouze při násobení a dělení (výsledek má v případě „fractional“ vždy stejný formát, jako vstup, tj. první bit je znaménkový, za ním následuje binární čárka a za ní 2N-1 bitů výsledku, kde N je šířka vstupních operandů).

9. Aritmeticko-logická jednotka a shifter

Aritmeticko-logická jednotka má v řadě Motorola 56000 poněkud odlišnou strukturu, než na jakou jsme zvyklí z běžných mikroprocesorů. ALU je zde totiž rozdělena na tři bloky – vlastní univerzální ALU, sčítačku a blok pro zaokrouhlení výsledků:

Obrázek 6: Struktura ALU (žluté bloky + zelená sčítačka).

Vidíme, že sčítačka dokáže vstupní operandy přečíst z násobičky, z akumulátorů či z vlastní ALU. Pokud se sčítá výstup z násobičky a akumulátorů (hodnota přečtená z akumulátoru může být bitově posunuta v shifteru), jedná se o operaci typu MAC (Multiply Accumulate) s 56bitovým výsledkem (48 bitů má součin, dalších osm bitů umožňuje provést až 255 MAC bez kontroly přetečení). Vstupní operand vypočtený ALU má šířku 48 bitů. Ve skutečnosti je struktura celého bloku poněkud složitější, protože na základě součtu či rozdílu provedeného ve sčítačce, se nastavují příznakové bity, což je ovšem téma, kterému se budeme věnovat příště.

10. Použití DSP řady Motorola 56000

Digitální signálové procesory Motorola 56000 jsou, a to i přesto, že se jedná o poměrně starou architekturu, prakticky používány dodnes. Jádra 56000 najdeme například v některých systémech pro zpracování audio signálu v reálném čase (tento čip má dostatečný výkon i pro MP3 kodeky). Ovšem zajímavé je i použití tohoto čipu v minulosti. Příkladem může být zabudování DSP řady 56000 do mnoha profesionálních zvukových karet Turtle Beach, použití v počítači Atari Falcon030, což byla na dobu vzniku unikátní kombinace (CPU Motorola 68030, volitelný FPU Motorola 68881/2 a DSP Motorola 56001), nebo do pracovních stanic Indigo firmy SGI. V počítači Atari Falcon byl sice DSP určen primárně pro zpracování zvuku, používal se však i pro dekompresi JPEG obrázků či pro renderování 3D grafiky (vznikla dokonce celá dema, jejichž grafická část běžela kompletně na DSP).

Obrázek 7: Profesionální karta pro zpracování zvuků, která je vybavena DSP Motorola 56000.

11. Doplněk na závěr – řada 56000 v porovnání s TMS320C10

Digitální signálové procesory Motorola 56000 byly po svém uvedení na trh velmi často porovnávány jak s již popsanými čipy firmy Texas Instruments TMS320, tak i s čipy od AT&T (tyto DSP byly používány pouze interně v této obří společnosti), Fujitsu (řada MB87×x), Hitachi (HD61810), NEC (řady µPD77×x) a taktéž Toshiba. Z následující tabulky je dobře patrné, jak se výkonnost digitálních signálových procesorů postupně zvyšovala:

| Čip | Rok vydání | ns/MAC | Mil.MACs/sec | Šířka operandů (zdroj/cíl) |

|---|---|---|---|---|

| TMS32010 | 1982 | 390 | 2,6 | 16/32 |

| TMS32020 | 1985 | 195 | 5,1 | 16/32 |

| TMS320C25 | 1987 | 100 | 10,0 | 16/32 |

| TMS320C30 | 1988 | 60 | 16,6 | 24/32 |

| DSP56001 | 1987 | 74 | 13,5 | 24/56 |

| DSP96002 | 1989 | 75 | 13,5 | 32/64 |

Poznámka: výkonnost DSP se uvádí buď v MIPS (což nemusí být nejdůležitější veličina), u procesorů s operacemi s plovoucí řádovou čárkou ve FLOPS (MFLOPS, GFLOPS) a taktéž v rychlosti provedení operací MAC (Multiply-Accumulate), což je v kontextu porovnávaných DSP mnohem důležitější veličina, protože tyto čipy jsou postaveny na rychlých násobičkách a sčítačkách. Aby bylo porovnání férové, jsou uvedeny i šířky zpracovávaných operandů (čtvrtý sloupec udává pouze čistě teoretický maximální výkon v milionech MAC za sekundu, praktický dosažitelný výkon bude vždy menší):

Obrázek 8: Zadní strana počítače Atari Falcon030 obsahuje mj. i konektor pro přístup k DSP i konektor rozhraní SCSI-II.

12. Odkazy na Internetu

- Motorola DSP56k

https://www.rockbox.org/wiki/MotorolaDSP56k - Motorola 56000 (Wikipedia)

http://en.wikipedia.org/wiki/Motorola_56000 - Using the Motorola DSP56002EVM for Amateur Radio DSP Projects

http://www.johanforrer.net/EVM/article.html - The Atari Falcon030 „Personal Integrated Media System“

http://www.atarimuseum.com/computers/16bits/falcon030.html - Turtle Beach Corporation (stránky společnosti)

http://www.turtlebeach.com/ - Turtle Beach Corporation (Wikipedia)

https://en.wikipedia.org/wiki/Turtle_Beach_Corporation - Atari Falcon 030 DSP 3D engine test

http://www.digiti.info/video/WHQwMjNRaExfLWs=/atari_falcon030_dsp_3d_engine_test - Atari Falcon030 (německy)

http://www.maedicke.de/atari/hardware/falcon.htm - Old-computers.com: Atari Falcon030

http://www.old-computers.com/museum/computer.asp?c=125&st=1 - Atari Falcon030 (Wikipedia)

http://en.wikipedia.org/wiki/Atari_Falcon - Past and current projects (including Falcon stuff)

http://os.inf.tu-dresden.de/~nf2/projects/projects.html - Atari Falcon 030: The Case For The Defence

http://www.soundonsound.com/sos/1994_articles/sep94/atarifalcon.html - DaVinci processor family

http://www.ti.com/general/docs/datasheetdiagram.tsp?genericPartNumber=TMS320DM365&diagramId=64193 - Texas Instruments DaVinci

https://en.wikipedia.org/wiki/Texas_Instruments_DaVinci - TMS320DM6446 (DaVinci)

http://www.ti.com/product/tms320dm6446 - Digital Media Video Processors (TI)

http://www.ti.com/lsds/ti/processors/dsp/media_processors/davinci/products.page# - TI Wiki

http://processors.wiki.ti.com/index.php/Main_Page - C5000 ultra-low-power DSP

http://www.ti.com/lsds/ti/processors/dsp/c5000_dsp/overview.page - OMAP (Wikipedia)

https://en.wikipedia.org/wiki/OMAP - OMAP – TI Wiki

http://processors.wiki.ti.com/index.php/OMAP - Why OMAP can't compete in smartphones

http://www.eetimes.com/author.asp?section_id=40&doc_id=1286602 - Applications Processors – The Heart of the Smartphone

http://www.engineering.com/ElectronicsDesign/ElectronicsDesignArticles/ArticleID/5791/Applications-Processors-The-Heart-of-the-Smartphone.aspx - TI cuts 1,700 jobs in OMAP shift

http://www.eetimes.com/document.asp?doc_id=1262782 - VLIW: Very Long Instruction Word: Texas Instruments TMS320C6×

http://www.ecs.umass.edu/ece/koren/architecture/VLIW/2/ti1.html - An Introduction To Very-Long Instruction Word (VLIW) Computer Architecture

Philips Semiconductors - VLIW Architectures for DSP: A Two-Part Lecture (PDF, slajdy)

http://www.bdti.com/MyBDTI/pubs/vliw_icspat99.pdf - Very long instruction word (Wikipedia)

https://en.wikipedia.org/wiki/Very_long_instruction_word - A VLIW Approach to Architecture, Compilers and Tools

http://www.vliw.org/book/ - VEX Toolchain (VEX = VLIW Example)

http://www.hpl.hp.com/downloads/vex/ - Elbrus (computer)

https://en.wikipedia.org/wiki/Elbrus_%28computer%29 - Super Harvard Architecture Single-Chip Computer

https://en.wikipedia.org/wiki/Super_Harvard_Architecture_Single-Chip_Computer - Digital Signal Processors (stránky TI)

http://www.ti.com/lsds/ti/processors/dsp/overview.page - C674× Low Power DSP (stránky TI)

http://www.ti.com/lsds/ti/processors/dsp/c6000_dsp/c674×/overview.page - TMS320C30 (stránky TI)

http://www.ti.com/product/tms320c30 - TMS320C6722B

http://www.ti.com/product/tms320c6722b/description - Introduction to DSP

http://www.ti.com/lit/wp/spry281/spry281.pdf - The Evolution of TMS (Family of DSPs)

http://www.slideshare.net/moto_modx/theevo1 - Datasheet k TMS32010

http://www.datasheetarchive.com/dlmain/49326c32a52050140abffe6f0ac4894aa09889/M/TMS32010 - 1979: Single Chip Digital Signal Processor Introduced

http://www.computerhistory.org/siliconengine/single-chip-digital-signal-processor-introduced/ - The TMS32010. The DSP chip that changed the destiny of a semiconductor giant

http://www.tihaa.org/historian/TMS32010–12.pdf - Texas Instruments TMS320 (Wikipedia)

https://en.wikipedia.org/wiki/Texas_Instruments_TMS320 - Great Microprocessors of the Past and Present: Part IX: Signetics 8×300, Early cambrian DSP ancestor (1978):

http://www.cpushack.com/CPU/cpu2.html#Sec2Part9 - Great Microprocessors of the Past and Present (V 13.4.0)

http://jbayko.sasktelwebsite.net/cpu.html - Introduction to DSP – DSP processors:

http://www.bores.com/courses/intro/chips/index.htm - The Scientist and Engineer's Guide to Digital Signal Processing:

http://www.dspguide.com/ - Digital signal processor (Wikipedia EN)

http://en.wikipedia.org/wiki/Digital_signal_processor - Digitální signálový procesor (Wikipedia CZ)

http://cs.wikipedia.org/wiki/Digitální_signálový_procesor - Digital Signal Processing FAQs

http://dspguru.com/dsp/faqs - Reprezentace numerických hodnot ve formátech FX a FP

http://www.root.cz/clanky/fixed-point-arithmetic/ - IEEE 754 a její příbuzenstvo: FP formáty

http://www.root.cz/clanky/norma-ieee-754-a-pribuzni-formaty-plovouci-radove-tecky/ - Čtyři základní způsoby uložení čísel pomocí FX formátů

http://www.root.cz/clanky/binarni-reprezentace-numerickych-hodnot-v-fx-formatu/ - Základní aritmetické operace prováděné v FX formátu

http://www.root.cz/clanky/zakladni-aritmeticke-operace-provadene-ve-formatu-fx/ - Aritmetické operace s hodnotami uloženými ve formátu FP

http://www.root.cz/clanky/aritmeticke-operace-s-hodnotami-ve-formatu-plovouci-radove-carky/ - FIR Filter FAQ

http://dspguru.com/dsp/faqs/fir - Finite impulse response (Wikipedia)

http://en.wikipedia.org/wiki/Finite_impulse_response - DSPRelated

http://www.dsprelated.com/ - Addressing mode (Wikipedia)

https://en.wikipedia.org/wiki/Addressing_mode - Orthogonal instruction set

https://en.wikipedia.org/wiki/Orthogonal_instruction_set - TI 16-bit and 32-bit microcontrollers

http://www.ti.com/lsds/ti/microcontrollers16-bit32-bit/overview.page - TMS 32010 Assembly Language Programmer's Guide (kniha na Amazonu)

https://www.amazon.com/32010-Assembly-Language-Programmers-Guide/dp/0904047423 - COSC2425: PC Architecture and Machine Language, PC Assembly Language

http://www.austincc.edu/rblack/courses/COSC2425/index.html