Obsah

1. Rozšíření instrukčních sad MIPS-3D a VIS

3. Datové typy (skaláry a vektory) použité v instrukční sadě MIPS-3D

4. Instrukce obsažené v sadě MIPS-3D

5. Použití instrukcí MIPS-3D v algoritmech počítačové grafiky

6. Operace dělení a výpočtu druhé odmocniny v instrukční sadě MIPS-3D

7. Instrukční sada VIS (Visual Instruction Set)

8. Datové typy používané instrukcemi VIS

1. Rozšíření instrukčních sad MIPS-3D a VIS

V předchozích dvou částech seriálu o architekturách počítačů jsme se zabývali popisem rozšiřujících instrukčních sad procesorů RISC, které byly do těchto čipů implementovány v rámci poměrně intenzivního rozvoje technologie SIMD, což je jedna z poněkud zjednodušených forem vektorových instrukcí. Prozatím jsme si popsali instrukční sadu MDMX (MadMax, MIPS Digital Media eXtension) pro čipy MIPS [1] a dále sady MAX-1 i MAX-2 určené pro procesory z rodiny PA-RISC [2]. Výčet instrukčních sad se SIMD instrukcemi na čipech RISC by však nebyl úplný, kdybychom zapomněli na instrukční sady VIS (Visual Instruction Set) pro mikroprocesory SPARC a na sadu MIPS-3D určenou – jak je z názvu patrné – pro čipy MIPS (zde se však jednalo o zcela jinou množinu instrukcí, než byla již popsaná sada MDMX, na některých mikroprocesorech se tyto sady mohly vhodně doplňovat).

Obrázek 1: Slavná Utažská čajová konvice (Utah teapot). V době vzniku instrukční sady MIPS-3D se ještě poměrně velké množství výpočtů nutných pro vykreslení této scény provádělo na mikroprocesoru; teprve později došlo k postupnému převodu většiny operací na grafický akcelerátor.

Pro připomenutí si ještě jednou ukažme tabulku s různými SIMD technologiemi používanými na čipech RISC:

| # | Zkratka/název | Plný název | Rodina procesorů |

|---|---|---|---|

| 1 | MAX-1 | Multimedia Acceleration eXtensions v1 | HP-PA RISC |

| 2 | MAX-2 | Multimedia Acceleration eXtensions v2 | HP-PA RISC |

| 3 | VIS 1 | Visual Instruction Set v1 | SPARC V9 |

| 4 | VIS 2 | Visual Instruction Set v2 | SPARC V9 |

| 5 | AltiVec | (obchodní názvy Velocity Engine, VMX) | PowerPC |

| 6 | MDMX | MIPS Digital Media eXtension (MaDMaX) | MIPS |

| 7 | MIPS-3D | MIPS-3D | MIPS |

| 8 | MVI | Motion Video Instructions | DEC Alpha |

| 9 | NEON | Advanced SIMD | Cortex (ARMv7) |

Obrázek 2: Trojrozměrná scéna vykreslená s využitím efektu mlhy (fog), který byl ve své nejjednodušší podobě implementován již na prvních grafických 3D akcelerátorech pro PC vybavených čipy 3dfx (Voodoo Graphics PCI).

2. Instrukční sada MIPS-3D

Nejprve se budeme zabývat instrukční sadou nazvanou příznačně MIPS-3D. Název této instrukční sady alespoň částečně naznačuje, jaké instrukce zde můžeme najít – jedná se o instrukce určené pro urychlení provádění některých operací typických pro 3D grafiku. Především se jedná o transformace, perspektivní promítání, normalizaci vektorů a ořezávání (clipping). V současnosti je sice možné provádění těchto operací přenechat grafickému akcelerátoru, ale v době vzniku technologie MIPS-3D byly grafické akcelerátory určeny především pro rasterizaci trojúhelníků a řešení viditelnosti pomocí paměti hloubky (Z-bufferu), zatímco základní zpracování trojrozměrné scény bylo ponecháno na mikroprocesoru; ostatně se můžeme sami podívat na postupný vývoj některých čipů určených pro použití na grafických akcelerátorech. Kromě prvního čipu se jedná o integrované obvody používané především na PC. Ty byly zhruba na přelomu tisíciletí nahrazeny výkonnějšími 3D akcelerátory druhé generace:

Akcelerátor/čipIntel i860 Voodoo Graphics PCIS3 Savage 3D Intel i740| # | Rok vydání |

|---|---|

| 1 | 1989 |

| 2 | 1996 |

| 3 | 1998 |

| 4 | 1998 |

Obrázek 3: Vykreslovací řetězec používaný grafickými akcelerátory při zpracovávání trojrozměrných scén. Do vykreslovacího řetězce vstupují dva typy dat – informace o vrcholech polygonů (trojúhelníků, plošných čtyřúhelníků atd.) a rastrová data, většinou bitmapy (znaky v rastrové podobě, bitové masky, sprity, kurzory myši) a především textury nanášené na vykreslované polygony.

Popisem mikroprocesorů z rodiny MIPS jsme se už v tomto seriálu zabývali, takže již víme, že se jednalo o procesory s typicky minimalistickou „RISCovou“ koncepcí, kdy se v instrukční pipeline prováděly všechny jednodušší aritmetické a logické instrukce, skoky i instrukce pro přenos dat mezi operační pamětí a pracovními registry. Mimo tuto pipeline byly prováděny některé složitější instrukce, typicky násobení. Pro aritmetické operace s hodnotami reprezentovanými v systému plovoucí řádové čárky (FP) byla použita zvláštní pipeline. Zcela stejný minimalistický princip byl použit i u instrukční sady MIPS, která je v porovnání s MMX, 3DNow! a samozřejmě též SSE velmi elegantní a přitom splňující daný účel.

Obrázek 4: Při výpočtu mlhy je nutné provést pro každý vykreslovaný fragment (fragment je, zjednodušeně řečeno, entita nesoucí informaci o jednom pixelu doplněnou o další atributy, například hloubku/vzdálenost fragmentu od pozorovatele) smíchání původní barvy fragmentu s barvou mlhy, přičemž poměr mezi původní barvou a barvou mlhy je určen na základě vzdálenosti fragmentu od pozorovatele a hustoty mlhy. Tato operace je v naprosté většině případů již prováděna na grafickém akcelerátoru, i když některé SIMD instrukce byly určeny pro zjednodušení těchto výpočtů.

3. Datové typy (skaláry a vektory) použité v instrukční sadě MIPS-3D

Podobně jako u popisů dalších instrukčních sad obsahujících SIMD instrukce, si i u technologie MIPS-3D nejprve popíšeme formát dat, se kterými se mohou provádět různé operace. MIPS-3D se v mnoha ohledech podobá již popsané sadě 3DNow! (přesněji řečeno je tomu spíše naopak :-), protože většina instrukcí je určena pro práci s vektory obsahujícími dvojici numerických hodnot reprezentovaných v systému plovoucí řádové čárky (floating point). Vzhledem k tomu, že každý prvek vektoru odpovídá 32bitovému datovému typu single či float, mají dvouprvkové vektory šířku 64 bitů a mohou se vejít do existujících 64bitových registrů matematického koprocesoru (což pro nás opět není žádná novinka). Ovšem kromě dvouprvkových vektorů jsou podporovány i další datové typy, které jsou i s příslušným označením (použitým dále) uvedeny v následující tabulce. Povšimněte si toho, že typy PL a PU reprezentují vždy jen jeden prvek vektoru a typ PW se od ostatních pěti typů liší v tom, že představuje dvouprvkový vektor celých hodnot (integer):

| # | Označení | Typ | Formát skaláru či vektoru | Stručný popis datového typu |

|---|---|---|---|---|

| 1 | S | skalár | 1×32 | datový typ single/float s plovoucí řádovou čárkou o šířce 32 bitů |

| 2 | D | skalár | 1×64 | datový typ double s plovoucí řádovou čárkou o šířce 64 bitů |

| 3 | PS | vektor | 2×32 | vektor obsahující dvojici prvků typu single, základ pro většinu 3D operací |

| 4 | PL | skalár | 1×32 | první/spodní prvek uložený v dvouprvkovém vektoru (single) |

| 5 | PU | skalár | 1×32 | druhý/horní prvek uložený v dvouprvkovém vektoru (single) |

| 6 | PW | vektor | 2×32 | dvě celočíselné hodnoty, každá o šířce 32 bitů |

Obrázek 5: Operace s fragmenty prováděné při rasterizaci trojúhelníků či obecnějších konvexních polygonů na grafickém akcelerátoru.

4. Instrukce obsažené v sadě MIPS-3D

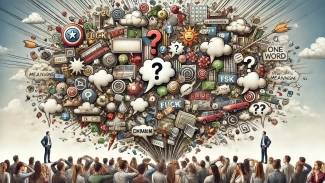

Instrukční sada MIPS-3D se od většiny podobných technologií zavádějících SIMD instrukce poměrně výrazně odlišuje v celkovém počtu instrukcí i v tom, jaké instrukce byly vybrány. Počet instrukcí je totiž roven pouze třinácti, ovšem s tím, že některé z těchto instrukcí mohou pracovat s různými datovými typy, takže se počet kombinací poněkud zvětšuje až na 23 možností. Zmíněných třináct instrukcí je možné podle jejich funkce rozdělit do čtyř kategorií – aritmetické instrukce, konverzní instrukce, instrukce porovnání (relace) a konečně instrukce pro provádění podmíněných skoků.

Obrázek 6: Rozdělení všech třinácti instrukcí MIPS-3D do čtyř skupin.

Všechny instrukce jsou vypsány v následující tabulce, kde je také pro každou instrukci uvedeno, s jakými datovými typy je možné tuto instrukci spustit (viz též tabulka uvedená v předchozí kapitole). Nyní již následuje slíbená tabulka:

| # | Kategorie | Instrukce | Datové typy | Popis |

|---|---|---|---|---|

| 1 | aritmetické | ADDR | PS | součet dvouprvkových vektorů |

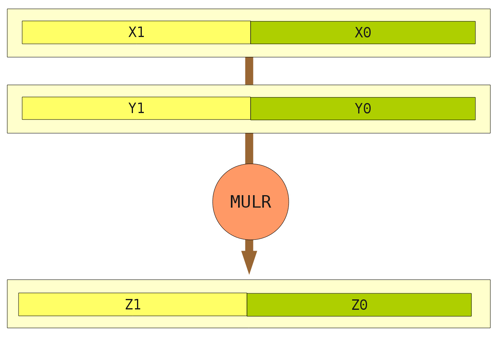

| 2 | aritmetické | MULR | PS | vynásobení prvků dvouprvkových vektorů |

| 3 | aritmetické | RECIP1 | S,D,PS | první (nepřesný ale rychlý) krok výpočtu převrácené hodnoty |

| 4 | aritmetické | RECIP2 | S,D,PS | zpřesnění výpočtu převrácené hodnoty |

| 5 | aritmetické | RSQRT1 | S,D,PS | první (nepřesný ale rychlý) krok výpočtu druhé odmocniny |

| 6 | aritmetické | RSQRT2 | S,D,PS | zpřesnění výpočtu druhé odmocniny |

| 7 | konverzní | CVT.PS.PW | PW→PS | konverze 32bitových celých čísel na dvojici FP hodnot |

| 8 | konverzní | CVT.PW.PS | PS→PW | konverze dvouprvkového vektoru FP hodnot na dvojici 32bitových celých čísel či čísel s pevnou čárkou |

| 9 | porovnání | CABS | S,D,PS | porovnání prvků vektorů či dvojice skalárních hodnot, jedna z nejdůležitějších operací připravujících příznaky pro podmíněné skoky |

| 10 | podmíněný skok | BC1ANY2F | × | skok v případě, že alespoň jeden ze dvou zvolených příznaků je nepravdivý (false), relativní 18bitová adresa |

| 11 | podmíněný skok | BC1ANY2T | × | skok v případě, že alespoň jeden ze dvou zvolených příznaků je pravdivý (true), relativní 18bitová adresa |

| 12 | podmíněný skok | BC1ANY4F | × | skok v případě, že alespoň jeden ze čtyř zvolených příznaků je nepravdivý (false), relativní 18bitová adresa |

| 13 | podmíněný skok | BC1ANY4T | × | skok v případě, že alespoň jeden ze čtyř zvolených příznaků je pravdivý (true), relativní 18bitová adresa |

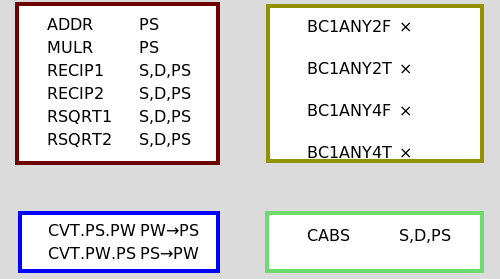

Obrázek 7: Instrukce ADDR pracuje s dvojicí vektorů, z nichž každý obsahuje dvě 32bitové hodnoty typu single/float.

5. Použití instrukcí MIPS-3D v algoritmech počítačové grafiky

Při pohledu na tabulku se seznamem instrukcí MIPS-3D uvedenou v předchozí kapitole se na první pohled může zdát, že instrukce byly vybírány náhodně. Ve skutečnosti to však není pravda, protože instrukční sada MIPS-3D byla naschvál navržena takovým způsobem, aby byla co nejjednodušší, což mj. jejím tvůrcům umožnilo se lépe soustředit na optimalizaci implementace všech instrukcí na čipu. Z toho například vyplývá i to, že se aritmetické instrukce zúžily na dvě základní operace součtu a násobku, které byly doplněny o výpočet převrácené hodnoty (základ pro dělení) a výpočet odmocniny, což zajisté není implementačně zcela jednoduchá operace, ovšem v počítačové grafice se odmocnina velmi často používá, typicky při výpočtu vzdálenosti a normalizacích vektorů.

V praxi je možné při implementaci algoritmů pro zpracování a vykreslování trojrozměrných scén využít instrukce ze sady MIPS-3D následujícím způsobem:

- Transformace vrcholů (vertexů) – ADDR

- Pohledové transformace – ADDR, MULR

- Ořezání (clipping) – CABS, BC* (podmíněné skoky)

- Normalizace vektorů – RECIP, RSQRT

- Perspektivní promítání – RECIP

- Odstranění odvrácených polygonů – ADDR, CABS, BC* (podmíněné skoky)

Obrázek 8: Instrukce MULR pracuje s dvojicí vektorů, z nichž každý obsahuje dvě 32bitové hodnoty.

6. Operace dělení a výpočtu druhé odmocniny v instrukční sadě MIPS-3D

Podívejme se nyní podrobněji na aritmetické instrukce RECIP1, RECIP2, RSQRT1 a RSQRT2. Jedná se o dvojici párů instrukcí, přičemž první pár tvořený instrukcemi RECIP1+RECIP2 je určen pro výpočet převrácené hodnoty s přesností specifikovanou programátorem a druhý pár RSQRT1+RSQRT2 slouží k výpočtu druhé odmocniny. V obou případech se jedná operace, které se v trojrozměrné počítačové grafice provádí poměrně často, typicky při normalizaci vektorů (při výpočtu osvětlení apod.) a taktéž při perspektivním promítání, protože výpočet převrácené hodnoty může být využit pro dělení, což je operace, která není v MIPS-3D implementována (a ve skutečnosti ani nemusí být). Po zavolání instrukce RECIP1 je převrácená hodnota vypočtena sice velmi rychle (se zpožděním jen o jeden takt), ovšem přesnost výpočtu je 14 bitů pro datový typ single a 23 bitů pro datový typ double. V případě, že programátorovi tato přesnost nedostačuje (někdy je ovšem více než dostatečná), může použít instrukci RECIP2 a výpočet tak dále zpřesnit podle svých požadavků (někdy je nutné zavolat RECIP2 i vícekrát).

Obrázek 9: Jednotka FPU je v procesorech UltraSPARC použita jak pro výpočty se skaláry (trojice bloků FP), tak i pro vektorové operace (dvojice bloků GR)

Uveďme si jednoduchý příklad: výpočet převrácené hodnoty s přesností minimálně 24 bitů (všechny výpočty se provádí s FPU registry pojmenovanými fx):

RECIP1.S f1, f0 ; přesnost výsledku jen 16 bitů (ovšem výpočet proveden rychle) RECIP2.S f2, f1, f0 MADD.S f3, f1, f1, f2 ; přesnost výsledku je nyní 24 bitů

Druhý příklad: výpočet převrácené hodnoty s přesností 52 bitů:

RECIP1.S f1, f0 ; přesnost výsledku jen 16 bitů (ovšem výpočet proveden rychle) RECIP2.D f2, f1, f0 MADD.D f3, f1, f1, f2 ; nyní již máme přesnost minimálně 32 bitů RECIP2.D f4, f3, f0 MADD.D f5, f3, f3, f4 ; a teď již plných 52 bitů

Podobné sekvence instrukcí lze použít i u dvojice operací RSQRT1 a RSQRT2. Opět se jedná o vědomou a svobodnou volbu mezi rychlostí výpočtu a jeho přesností.

Poznámka: připomeňme si, že o podobné technologii jsme se již zmiňovali při popisu dnes již poněkud neprávem opomíjené instrukční sady 3DNow!, která mj. obsahovala i instrukce PFRCP, PFRSQRT, PFRCPIT1, PFRSQIT1 a PFRCPIT2 s významem podobným, jako je tomu u výše uvedených instrukcí RECIP1, RECIP2, RSQRT1 a RSQRT2.

Obrázek 10: Jeden z formátů vektorové operace násobení nabízený instrukční sadou VIS.

7. Instrukční sada VIS (Visual Instruction Set)

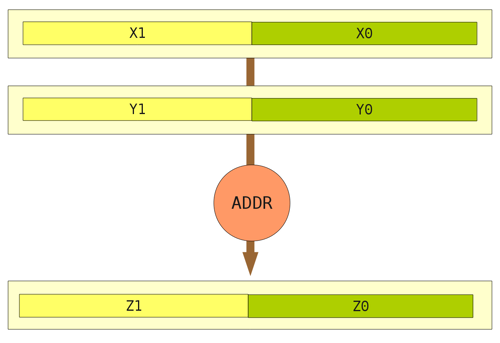

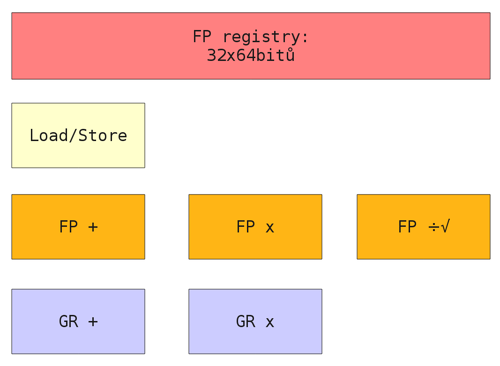

Po popisu technologie MIPS-3D se ve zbývajících dvou kapitolách budeme zabývat technologií určenou pro konkurenční mikroprocesory z rodiny UltraSPARC. Jedná se o technologii nazvanou VIS, což je zkratka plného názvu „Visual Instruction Set“. Instrukční sada VIS se v mnoha ohledech odlišuje od výše popsané sady MIPS-3D, což však není překvapivé, protože se jedná o instrukční sadu určenou pro jiné účely. V rámci VIS byly mikroprocesory UltraSPARC obohaceny o přibližně padesát nových instrukcí, které implementovaly aritmetické operace, logické operace, rozbalení a zabalení dat ve vektorech, změnu zarovnání dat ve vektorech, datové konverze a na závěr i operace zjednodušující adresování jednorozměrných, dvourozměrných a trojrozměrných polí. Nesmíme zapomenout ani na blokové operace, které v době vzniku této technologie umožňovaly blokový přenos dat rychlostí až 300 MB/sekundu, a to při libovolném zarovnání.

Obrázek 11: Porovnávání šestnáctibitových prvků vektorů s nastavením čtveřice bitových příznaků. Instrukce, která toto porovnání provádí, se jmenuje fcmp*16, přičemž za hvězdičku lze dosadit gt, ge, eq atd.

Společně s novými instrukcemi byl rozšířen i počet funkčních modulů matematického koprocesoru. Ten byl rozdělen na šest základních modulů pracujících nezávisle na sobě:

| # | Označení modulu | Popis funkce modulu |

|---|---|---|

| 1 | FP + | součet skalárních hodnot typu single/float a double |

| 2 | FP × | součin skalárních hodnot typu single/float a double |

| 3 | FP ÷ √ | výpočet podílu a druhé odmocniny (prováděno mimo instrukční pipeline – out of order) |

| 4 | GR + | součet dvou vektorů s různými formáty (interně se jedná o čtveřici ALU + shifter) |

| 5 | GR × | součin dvou vektorů s různými formáty |

| 6 | Load/Store | přenos dat z a do operační paměti |

Díky internímu uspořádání matematického koprocesoru bylo možné současně provádět dvě aritmetické operace součtu a součinu a navíc ve stejný okamžik ukládat či načítat hodnotu z operační paměti. Dělení a výpočet druhé odmocniny se prováděl mimo instrukční pipeline (out of order). Podobně tomu bylo u obou „grafických“ modulů – pro součet se využíval modul s klasickou pipeline, tj. v každém taktu bylo možné dokončit jednu operaci (prováděnou nad celým vektorem), zatímco násobení prvků vektorů trvalo o tři takty déle, ovšem bylo ho možné provádět paralelně a nezávisle na ostatních probíhajících operacích.

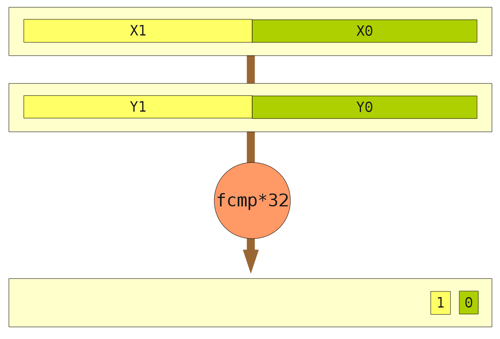

Obrázek 12: Porovnávání třicetidvoubitových prvků vektorů s nastavením dvojice bitových příznaků. Instrukce, která toto porovnání provádí, se jmenuje fcmp*32, přičemž za hvězdičku lze dosadit gt, ge, eq atd., podobně jako u předchozí instrukce fcmp*16

8. Datové typy používané instrukcemi VIS

Podobně jako u technologií MIPS-3D, MMX či 3DNow! se i v případě technologie VIS všechny operace prováděly s registry určenými původně pro matematický koprocesor, což samozřejmě souvisí i s interní strukturou mikroprocesoru zmíněnou v předchozí kapitole. Registrů používaných matematickým koprocesorem je celkem 32 a každý z nich má šířku 64 bitů, což odpovídá datovému typu double. Pro účely operací nad vektory využívanými jak v 2D, tak i v 3D počítačové grafice byly v rámci technologie VIS vytvořeny další tři datové struktury (vektory):

- 2×32 bitů (celá čísla se znaménkem nebo bez znaménka, též typ float/single)

- 4×16 bitů (celá čísla se znaménkem nebo bez znaménka)

- 8×8 bitů (celá čísla se znaménkem nebo bez znaménka)

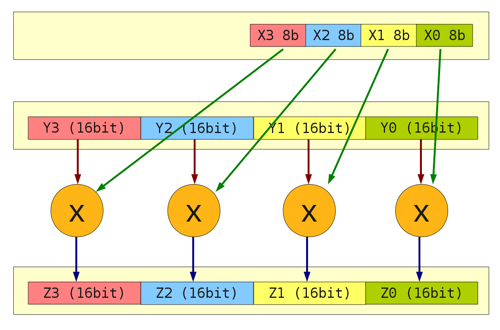

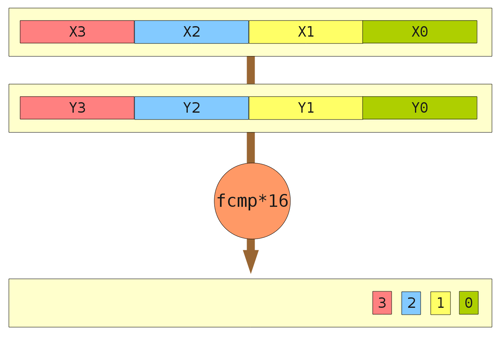

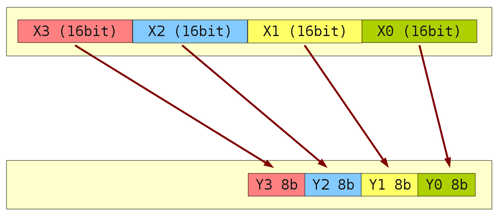

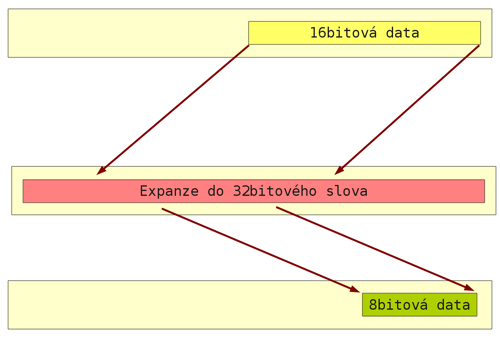

Instrukční sada VIS obsahuje velké množství instrukcí určených pro provádění různých operací s rastrovými daty. Typicky se jedná o operaci násobení vektoru s osmibitovými hodnotami (barvovými složkami jednotlivých pixelů), což je operace používaná například při alpha blendingu (prolínání dvou obrázků s postupnou změnou jejich průhlednosti), ale taktéž při diskrétní kosinové transformaci využívané ve formátech JPEG/JFIF a MPEG. Mnoho instrukcí je určeno pro konverze dat – viz též naznačení funkce těchto instrukcí na poslední trojici obrázků. Při těchto operacích se poměrně intenzivně využívá shifter zapojený za čtveřicí aritmeticko-logických jednotek.

Obrázek 13: Jednoduchá konverzní operace – změna šířky prvků vektoru z 16 bitů na 8 bitů s volitelným zachováním znaménka.

To znamená, že (nejenom) z tohoto pohledu se technologie VIS podobá již dříve popsané technologii MMX, což je možná i pochopitelné, protože tyto technologie vznikly zhruba ve stejnou dobu. Firma Sun Microsystems (ještě v době své slávy) totiž představila VIS již v roce 1994 a poprvé ji do praxe zavedla v roce 1995 společně s mikroprocesory UltraSPARC, zatímco společnost Intel přišla s technologií MMX až o rok později. Dodejme ještě, že pro rodinu SPARC64 se VIS použila v roce 2000 a druhá verze instrukční sady označovaná jako VIS 2 byla implementována v mikroprocesorech UltraSPARC III. Ovšem z praktického hlediska je mezi oběma zmiňovanými technologiemi přece jen jeden dosti podstatný rozdíl – MMX může využívat pouze osmici 64bitových registrů, zatímco překladače určené pro UltraSPARC a VIS mohou své programy optimalizovat na využití celé sady 32 registrů, každého o šířce 64 bitů.

Obrázek 14: Ukázka jedné z mnoha konverzních operací, které lze provádět díky instrukční sadě VIS. Umístění načtených 16bitových dat v 32bitovém slově lze v určité míře měnit.

9. Odkazy na Internetu

- MIPS-3D® ASE

http://www.mips.com/products/architectures/mips-3d-ase/ - An introduction to SPARC's SIMD offerings

http://mikeburrell.wordpress.com/2007/12/14/an-introduction-to-sparcs-simd-offerings/ - MIPS64TM Architecture for Programmers Volume IV-c: The MIPS-3DTM Application-Specific Extension to the MIPS64TM

http://www.weblearn.hs-bremen.de/risse/RST/docs/MIPS/MD00099–2B-MIPS3D64-AFP-01.11.pdf - Visual Instruction Set

http://www.enotes.com/topic/Visual_Instruction_Set - NEON

http://www.arm.com/products/processors/technologies/neon.php - Architecture and Implementation of the ARM Cortex-A8 Microprocessor

http://www.design-reuse.com/articles/11580/architecture-and-implementation-of-the-arm-cortex-a8-microprocessor.html - Multimedia Acceleration eXtensions (Wikipedia)

http://en.wikipedia.org/wiki/Multimedia_Acceleration_eXtensions - AltiVec (Wikipedia)

http://en.wikipedia.org/wiki/AltiVec - Visual Instruction Set (Wikipedia)

http://en.wikipedia.org/wiki/Visual_Instruction_Set - MAJC (Wikipedia)

http://en.wikipedia.org/wiki/MAJC - MDMX (Wikipedia)

http://en.wikipedia.org/wiki/MDMX - MIPS Multiply Unit

http://programmedlessons.org/AssemblyTutorial/Chapter-14/ass14_3.html - Silicon Graphics Introduces Enhanced MIPS Architecture

http://bwrc.eecs.berkeley.edu/CIC/otherpr/enhanced_mips.html - MIPS-3D (Wikipedia)

http://en.wikipedia.org/wiki/MIPS-3D - MIPS Technologies, Inc. announces new MIPS-3D technology to provide silicon-efficient 3D graphics acceleration

http://www.design-reuse.com/news/2057/mips-mips-3d-technology-silicon-efficient-3d-graphics-acceleration.html - MIPS-3D Built-in Function (gcc.gnu.org)

http://gcc.gnu.org/onlinedocs/gcc/MIPS_002d3D-Built_002din-Functions.html - Baha Guclu Dundar:

Intel MMX, SSE, SSE2, SSE3/SSSE3/SSE4 Architectures - SSE (Streaming SIMD Extentions)

http://www.songho.ca/misc/sse/sse.html - Timothy A. Chagnon: SSE and SSE2

http://www.cs.drexel.edu/~tc365/mpi-wht/sse.pdf - Intel corporation: Extending the Worldr's Most Popular Processor Architecture

http://download.intel.com/technology/architecture/new-instructions-paper.pdf - SIMD architectures:

http://arstechnica.com/old/content/2000/03/simd.ars/ - Tour of the Black Holes of Computing!: Floating Point

http://www.cs.hmc.edu/~geoff/classes/hmc.cs105…/slides/class02_floats.ppt - 3Dnow! Technology Manual

AMD Inc., 2000 - Intel MMXTM Technology Overview

Intel corporation, 1996 - MultiMedia eXtensions

http://softpixel.com/~cwright/programming/simd/mmx.phpi - AMD K5 („K5“ / „5k86“)

http://www.pcguide.com/ref/cpu/fam/g5K5-c.html - Sixth Generation Processors

http://www.pcguide.com/ref/cpu/fam/g6.htm - Great Microprocessors of the Past and Present

http://www.cpushack.com/CPU/cpu1.html - Very long instruction word (Wikipedia)

http://en.wikipedia.org/wiki/Very_long_instruction_word - CPU design (Wikipedia)

http://en.wikipedia.org/wiki/CPU_design - Control unit (Wikipedia)

http://en.wikipedia.org/wiki/Control_unit - Cray History

http://www.cray.com/About/History.aspx?404;http://www.cray.com:80/about_cray/history.html - Cray Historical Timeline

http://www.cray.com/Assets/PDF/about/CrayTimeline.pdf - Computer Speed Claims 1980 to 1996

http://homepage.virgin.net/roy.longbottom/mips.htm - Superpočítače Cray

http://www.root.cz/clanky/superpocitace-cray/ - Superpočítače Cray (druhá část)

http://www.root.cz/clanky/superpocitace-cray-druha-cast/ - Superpočítače Cray (třetí část)

http://www.root.cz/clanky/superpocitace-cray-treti-cast/ - Superpočítače Cray (čtvrtá část)

http://www.root.cz/clanky/superpocitace-cray-ctvrta-cast/ - Superpočítače Cray (pátá část): architektura Cray X-MP

http://www.root.cz/clanky/superpocitace-cray-pata-cast-architektura-pocitace-cray-x-mp-a-jeho-pouziti-ve-filmovem-prumyslu/