Obsah

1. Mikrořadičová jádra TriCore: kombinace MCU, DSP a RISCu

3. Pracovní a adresové registry

6. Instrukční soubor jader TriCore

7. Podskupina šestnáctibitových instrukcí

9. Aritmetické instrukce s podmínkou

11. Operace MAC (Multiply-Accumulate)

13. Instrukce SEL – Conditional Select

14. SIMD neboli operace s krátkými vektory

1. Mikrořadičová jádra TriCore: kombinace MCU, DSP a RISCu

Pro ty aplikace, v nichž je nutné zkombinovat schopnosti výkonného mikrořadiče a digitálního signálového procesoru, navrhla společnost Infineon čipy nazvané TriCore, jejichž součástí je 32bitové RISCové jádro se šestnácti datovými a šestnácti adresovými registry doplněné o digitální signálový procesor a taktéž o instrukce, které si většinou spojujeme s klasickými mikrořadiči (operace nad jednotlivými bity atd.). Instrukční soubor je unifikovaný a je založen na 32bitové RISCové instrukční sadě (i když ne tak jednoduché a přímočaré, jako je tomu u architektur RISC či MIPS) zkombinované s vybranými instrukcemi, které jsou zakódovány do šestnáctibitových instrukčních slov. Díky tomu je možné vyvíjet a především kombinovat jak výkonné algoritmy s většími nároky na programovou paměť (a vyrovnávací paměť), tak i ty části programu, kde je dbán větší důraz na efektivní využití programové paměti.

Zajímavé je porovnání jader TriCore s již popsanými čipy OMAP a DaVinci navrženými společností Texas Instruments. Zatímco v případě OMAP a DaVinci jsou použity dva oddělené a samostatně pracující subsystémy – procesor ARM a digitální signálový procesor (s vlastními akumulátory apod.) – je v případě TriCore hlavní procesorové jádro a DSP integrováno do jednoho celku, takže sice pracuje samostatně, ovšem DSP využívá stejné pracovní registry jako RISCové jádro. Navíc je unifikován i instrukční soubor, což do značné míry zjednodušuje vývoj aplikací (je ovšem na druhou stranu značně závislý na schopnostech céčkového překladače, pokud se programátoři neuchýlí k použití assembleru).

Obrázek 1: Modulární struktura čipů DaVinci.

2. Plně 32bitové jádro

Jádro TriCore je plně 32bitové, což se projevilo jak na šířce zpracovávaných dat (a to včetně operandů vstupujících do modulu DSP), tak i na možnosti adresování (programu i dat). Procesor dokáže bez problémů adresovat až 4 GB paměti, takže se zde nesetkáme s problémy, které museli řešit tvůrci šestnáctibitových čipů, například minule popsaných jader C166S V2 (už vůbec nemluvě o jádrech osmibitových, například o řadě XC800). I instrukční soubor je navržen takovým způsobem, že všechny instrukce mají 32bitová instrukční slova (RISCový přístup), ovšem s tím, že u vybrané skupiny instrukcí existuje ještě zkrácený šestnáctibitový formát, který je možné používat paralelně s formátem 32bitovým.

3. Pracovní a adresové registry

Jádra TriCore obsahují celkem šestnáct pracovních registrů, z nichž každý má šířku 32 bitů (u některých instrukcí se však pracuje jen s horní či dolní polovinou pracovního registru, zápis je následující: DnU a DnL). Tyto registry se jmenují D0 až D15 a jsou podle tzv. kontextu rozděleny do dvou skupin. Poslední – šestnáctý – registr D15 je současně i implicitním registrem pro některé operace, v nichž nejsou všechny registry zmíněny explicitně (jedná se především o šestnáctibitové operace zmíněné dále):

| Registr | Šířka | Kontext | Plné jméno | Význam |

|---|---|---|---|---|

| D0 | 32 bitů | L | Data Register | pracovní (datový) registr |

| D1 | 32 bitů | L | Data Register | -//- |

| D2 | 32 bitů | L | Data Register | -//- |

| D3 | 32 bitů | L | Data Register | -//- |

| D4 | 32 bitů | L | Data Register | -//- |

| D5 | 32 bitů | L | Data Register | -//- |

| D6 | 32 bitů | L | Data Register | -//- |

| D7 | 32 bitů | L | Data Register | -//- |

| D8 | 32 bitů | U | Data Register | -//- |

| D9 | 32 bitů | U | Data Register | -//- |

| D10 | 32 bitů | U | Data Register | -//- |

| D11 | 32 bitů | U | Data Register | -//- |

| D12 | 32 bitů | U | Data Register | -//- |

| D13 | 32 bitů | U | Data Register | -//- |

| D14 | 32 bitů | U | Data Register | -//- |

| D15 | 32 bitů | U | Implicit Data Register | implicitní datový registr pro některé operace |

Ve sloupci „Kontext“ je uvedeno, jestli pracovní registr náleží do takzvaného „Upper contextu“ nebo naopak do „Lower contextu“. V instrukční sadě totiž nalezneme několik instrukcí určených pro rychlé uložení kontextu (tj. všech registrů do něj patřících) a samozřejmě i pro obnovení kontextu. Příkladem mohou být přerušovací rutiny, které mohou pracovat jen s registry náležejícími do dolního kontextu. Na začátku takové rutiny bude instrukce SVLCX (Store Lower Context) nebo BISR (Begin Interrupt Service Routine), na konci pak instrukce RSLCX (Restore Lower Context).

Kromě šestnácti pracovních registrů najdeme v jádrech TriCore i šestnáct registrů adresových. Tyto registry nesou názvy A0 až A15. Některé registry z této sady mají speciální význam, což se týká především registru A10 sloužícího jako ukazatel na vrchol zásobníku a taktéž registru A11 s návratovou adresou. I adresové registry jsou rozděleny podle kontextu, ovšem do každého kontextu spadá pouze šest adresových registrů, nikoli osm:

| Registr | Šířka | Kontext | Plné jméno | Význam |

|---|---|---|---|---|

| A0 | 32 bitů | – | Global Address Register | není obnoven při návratu z ISR |

| A1 | 32 bitů | – | Global Address Register | není obnoven při návratu z ISR |

| A2 | 32 bitů | L | Address Register | |

| A3 | 32 bitů | L | Address Register | |

| A4 | 32 bitů | L | Address Register | |

| A5 | 32 bitů | L | Address Register | |

| A6 | 32 bitů | L | Address Register | |

| A7 | 32 bitů | L | Address Register | |

| A8 | 32 bitů | – | Global Address Register | není obnoven při návratu z ISR |

| A9 | 32 bitů | – | Global Address Register | není obnoven při návratu z ISR |

| A10 | 32 bitů | U | Stack Return Register | použit jako ukazatel na vrchol zásobníku |

| A11 | 32 bitů | U | Return Address Register | obsahuje návratovou adresu |

| A12 | 32 bitů | U | Address Register | |

| A13 | 32 bitů | U | Address Register | |

| A14 | 32 bitů | U | Address Register | |

| A15 | 32 bitů | U | Implicit Base Address Register | implicitní adresový registr |

Povšimněte si, že všechny čtyři registry Global Address Register nepatří do žádného kontextu. Tyto registry jsou typicky používány operačním systémem; pokud se používají i v běžných programech, je nutné ošetřit, aby se obnovovala jejich původní hodnota.

4. Stavové a řídicí registry

Sada stavových a řídicích registrů je u jader TriCore poměrně malá, protože zde najdeme jen klasický 32bitový programový čítač, stavový registr a taktéž registr PCXI s informacemi o předchozím kontextu. Ovšem kromě těchto tří registrů se u většiny čipů s jádrem TriCore nachází i sada speciálních funkčních registrů (SFR), kterých může být podle množství periferních modulů (porty, sběrnice, čítače, watchdogy, převodníky) i několik set:

| Registr | Šířka | Kontext | Plné jméno |

|---|---|---|---|

| PC | 32 bitů | L | Program Counter |

| PSW | 32 bitů | U | Procesor Status Word |

| PCXI | 32 bitů | U | Previous Context Information Register |

Příznaky je možné ze stavového registru přenést instrukcí MFCR (Move From Core Register), zpětný zápis se provádí instrukcí MTCR (Move To Core Register). Tyto instrukce pracují i s ostatními speciálními funkčními registry.

5. DSP Modul

Součástí jader TriCore je i modul DSP, který je mj. osazen rychlou násobičkou, sčítačkou a barrel shifterem. Tento modul dokáže v každém taktu dokončit jednu operaci MAC (Multiply Accumulate) s šestnáctibitovými vstupními operandy a s volitelnou saturací výsledku (po součtu). Mezi operace prováděné DSP modulem patří:

- Vynásobení dvou šestnáctibitových operandů uložených ve formátu Q15 (viz další text).

- Automatické posunutí výsledku násobení (tím je 32bitová hodnota).

- Součet vynásobeného výsledku s hodnotou uloženou v akumulátoru. V tomto případě se používá jen jediný „hlídací“ (guard) bit pro otestování přetečení.

- Alternativně je možné akumulovaný výsledek uložit do dvojice registrů a získat tak 64bitový akumulátor.

- Zaokrouhlení výsledku při převodu zpět na 16bitovou hodnotu.

- Řízení režimu akumulace – s přetečením či se saturací.

Zajímavé jsou formáty dat, s nimiž DSP modul pracuje. Základní formát se jmenuje Q15; jedná se o šestnáctibitové slovo, v jehož nejvyšším bitu je uloženo znaménko a v dalších patnácti bitech pak binární číslice ZA řádovou tečkou (jedná se o tečku dvojkovou, nikoli desetinnou). I z tohoto důvodu se tento formát také označuje 1.15 či fractional:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+ |s , | +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

Minimální reprezentovatelná hodnota je rovna přesně –1, což odpovídá 16bitovému slovu s bitovým vzorkem 0×8000:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+ |-1, 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0| +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

Maximální hodnota je rovna 1–2-15=.9999694825 (tedy „skoro jedna“) a odpovídá 16bitovému slovu s bitovým vzorkem 0×7fff:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+ | 0, 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1| +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

Druhý formát je prakticky totožný, ovšem počet binárních číslic za řádovou tečkou je roven 31 (formát 1.31 či Q31):

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+ |s , | +--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

Existuje ještě meziformát 2.30 získaný násobením dvou hodnot ve formátu 1.15, v němž je za řádovou tečkou 30 binárních číslic a před tečkou dva bity. Tento meziformát dokáže reprezentovat i hodnotu 1,0 získanou vynásobením –1,0×-1,0 (toto je vlastně jediná hodnota, která by mohla způsobovat problémy).

6. Instrukční soubor jader TriCore

Instrukce zpracovávané jádry TriCore jsou sice v některých ohledech odvozeny od klasických RISCových instrukčních sad, ovšem kvůli zařazení DSP operací, dále popsaných šestnáctibitových instrukcí atd. je ve skutečnosti instrukční sada poměrně komplikovaná. Všechny instrukce můžeme rozdělit do několika kategorií popř. podkategorií:

- Aritmetické instrukce

- Celočíselné

- DSP

- SIMD

- Adresová aritmetika

- Logické instrukce

- Manipulace s jednotlivými bity

- Přenosy dat

- Přenosy dat mezi registry

- Podmíněné přenosy dat (CMOV)

- Load/Store

- Porovnání hodnot či adres

- Skoky

- Nepodmíněné

- Podmíněné

- Instrukce pro programové smyčky

- Podmnožina šestnáctibitových instrukcí

- Systémové instrukce (začátek rutiny pro obsluhu přerušení, debug režim …)

Poznámka: v následujících kapitolách si popíšeme jen poměrně omezenou sadu vybraných instrukcí. Podrobnější popis instrukční sady, adresovacích režimů apod. bude uveden až v navazujícím článku

7. Podskupina šestnáctibitových instrukcí

Jádra TriCore kromě běžných (pseudo)RISCových instrukcí s 32bitovým instrukčním slovem obsahují i podskupinu instrukcí, jejichž šířka je poloviční (šestnáct bitů). Prefixy těchto instrukcí se odlišují od 32bitových instrukcí, takže je možné obě skupiny instrukcí libovolným způsobem mixovat, na rozdíl od režimů ARM a Thumb známých z mikroprocesorů a mikrořadičů ARM. Díky rozšíření instrukční sady o instrukce s šířkou šestnácti bitů je umožněno snížení velikosti programu o přibližně jednu třetinu.

Kvůli zmenšení velikosti instrukčních slov na polovinu bylo nutné v šestnáctibitových instrukcích udělat mnoho kompromisů, například:

- Konstanty v instrukcích mohou mít jen nízké hodnoty.

- Offsety při adresování jsou taktéž menší.

- Při určování registrů je kombinuje jeden zdrojový registr s registrem cílovým (dva operandy, nikoli tři).

- V některých případech se používá implicitní datový registrD15.

- Podobně to platí i u implicitního adresového registruA15.

Skupina šestnáctibitových instrukcí je poměrně malá, což je ostatně patrné z následující tabulky:

| Aritmetické instrukce | ADD, ADDSC, SUB, CADD, CADDN, SAT |

| Logické instrukce | AND, OR |

| Posuny | SH, SHA |

| Porovnání | EQ, LT |

| Přenosy dat a podmíněné přenosy dat | MOV, CMOV, CMOVN |

| Skoky (podmíněné i nepodmíněné) | J, JEQ, JGEZ, JGTZ, JI, JLEZ, JLTZ, JNE, JNZ, JZ |

| Implementace programových smyček | LOOP, LOOPU |

| Ostatní instrukce | BISR, BSPLIT, DEBUG, NOP, RET, RFE, ST |

8. Aritmetické instrukce

Sada aritmetických instrukcí je poměrně rozsáhlá, protože kromě běžných instrukcí zde najdeme i varianty součtu a rozdílu prováděných se saturací (jak se znaménkem, tak bez znaménka). Navíc je možné zvolit, jakým způsobem se bude pracovat s příznakem carry (přenos), který je součástí stavového registru PSW. Pokud je totiž zapotřebí implementovat víceslovní aritmetiku, je první součet proveden instrukcí ADDX (Add Extended) nastavující příznak carry a další slova pak sčítat instrukcí ADDC (Add with Carry). Pokud je zapotřebí přičíst k obsahu vybraného registru konstantu, lze zvolit instrukci ADDI pro přičtení 16bitové konstanty popř. instrukci ADDIH pro přičtení taktéž šestnáctibitové konstanty, ovšem posunuté o šestnáct bitů doleva (takže se přičítá k hornímu půlslovu). Důvod k existenci dvou instrukcí namísto instrukce jediné (s 32bitovou konstantou) je u všech RISCových procesorů stejný – instrukční kód i vlastní konstanta se musí nějakým způsobem vměstnat do „pouhých“ třiceti dvou bitů instrukčního slova.

9. Aritmetické instrukce s podmínkou

Užitečné jsou i aritmetické instrukce s podmínkou, protože díky jejich existenci je možné do jisté míry omezit počet podmíněných skoků (se všemi problémy, které jejich použití v RISCových jádrech přináší). Tyto instrukce nejdříve otestují obsah vybraného pracovního registru – nenulová hodnota je považována za true, nulová hodnota za false (tedy opět stejně, jako je tomu v céčku). Mezi aritmetické instrukce s podmínkou patří především:

| Instrukce | Význam |

|---|---|

| CADD | součet, pokud je obsah vybraného pracovního registru nenulový |

| CADDN | součet, pokud je obsah vybraného pracovního registru nulový |

| CSUB | rozdíl, pokud je obsah vybraného pracovního registru nenulový |

| CSUBN | rozdíl, pokud je obsah vybraného pracovního registru nulový |

10. Násobení

Pro násobení – což jsou instrukce oddělené od DSP modulu (jsou totiž prováděné v aritmeticko-logické jednotce) – se používají tyto tři instrukce s 32bitovým či 64bitovým výsledkem:

| Instrukce | Význam |

|---|---|

| MUL | násobení dvou hodnot se znaménkem (s 32bitovým či 64bitovým výsledkem) |

| MULS | násobení dvou hodnot se znaménkem a se saturací |

| MULS.U | násobení dvou hodnot bez znaménka a se saturací |

Šířka výsledku je určena na základě typů operandů. Tyto instrukce produkují výsledky kompatibilní s céčkovskou operací * aplikovanou na celá čísla (na rozdíl od instrukcí popsaných v navazující kapitole).

11. Operace MAC (Multiply-Accumulate)

Již výše zmíněná jednotka určená pro DSP operace je podporována instrukcemi MUL.Q (Multiply Q format), MULR.Q (Multiply Q format with Rounding), MADD.Q (Multiply-Add Q format), MADDS.Q (Multiply-Add Q format with Saturation) a variantami MADD.Q se zaokrouhlením. Šířka vstupních i výstupních dat je určena z typů operandů:

| Vstupní operand | Vstupní operand | Výstupní operand | Výpočet |

|---|---|---|---|

| DnU | DmU | Dz | 16×16 → 32 |

| DnL | DmL | Dz | 16×16 → 32 |

| DnU | Dm | Dz | 16×32 → 32 |

| DnL | Dm | Dz | 16×32 → 32 |

| Dn | Dm | Dz | 32×32 → 32 |

| DnU | Dm | Ez | 16×32 → 64 |

| DnL | Dm | Ez | 16×32 → 64 |

| Dn | Dm | Ez | 32×32 → 64 |

Značení vstupních a výstupních operandů je následující:

- Běžný pracovní registr se v assembleru zapisuje Dn, kde n=0..15.

- Spodní polovina pracovního registru Dn se zapisuje DnL.

- Horní polovina pracovního registru Dn se zapisuje DnU.

- Registrový pár Dn+1 | Dn se zapisuje En.

Poznámka: povšimněte si další zajímavé vlastnosti jader TriCore – jádro DSP je plně integrováno do hlavního procesoru a nenachází se zde žádné speciální vstupní registry do DSP, akumulátory atd. Z pohledu programátora se tedy jedná o velmi snadno použitelný čip, na rozdíl od (např.) čipů OMAP, kde je DSP od ARMovského jádra odděleno.

12. Dělení

Dělení je složitější, neboť se celá operace rozděluje do několika kroků. Při inicializaci si dělička připravuje obsahy interních registrů používaných při dělení, provádí konverze (bitové posuny) atd. Následuje jeden až čtyři kroky dělení, přičemž se v každém kroku vyprodukuje osm bitů výsledku. Na závěr je někdy nutné provést instrukci DVADJ; tu lze vynechat ve chvíli, kdy je jisté, že je dělenec i dělitel kladný:

| Instrukce | Význam |

|---|---|

| DVINIT | inicializace děličky (očekává se 32bitový podíl, dělení se znaménkem) |

| DVINIT.H | inicializace děličky (očekává se 16bitový podíl, dělení se znaménkem) |

| DVINIT.B | inicializace děličky (očekává se osmibitový podíl, dělení se znaménkem) |

| DVINIT.U | inicializace děličky (očekává se 32bitový podíl, dělení bez znaménka) |

| DVINIT.HU | inicializace děličky (očekává se 16bitový podíl, dělení bez znaménka) |

| DVINIT.BU | inicializace děličky (očekává se osmibitový podíl, dělení bez znaménka) |

| DVSTEP | jeden krok dělení, který vyprodukuje osm bitů výsledku (tento krok se opakuje 1×, 2×, 4×) |

| DVSTEP.U | jeden krok dělení, který vyprodukuje osm bitů výsledku (tento krok se opakuje 1×, 2×, 4×) |

| DVADJ | nutné provést pro dělení se znaménkem, když dělenec či dělitel může být záporný |

Rozdělení do několika kroků je vynuceno typickým použitím jader TriCore – je nutné rychle reagovat na přerušení, takže si většinou vývojáři nemohou dovolit, aby nějaká instrukce trvala příliš dlouho.

13. Instrukce SEL – Conditional Select

Další užitečnou instrukcí s podmínkou (testem nulovosti či nenulovosti datového registru) je instrukce zapisovaná mnemotechnickým kódem SEL neboli (Conditional) Select. Tato instrukce pracuje následovně: pokud je podmínka splněna, uloží se do zvoleného cílového registru hodnota z prvního zdrojového registru. Pokud podmínka naopak splněna není, je do cílového registru uložena hodnota z druhého zdrojového registru. Jinými slovy to znamená, že instrukce SEL nahrazuje programovou konstrukci typu:

cíl = condition ? zdroj1 : zdroj2;

Pokud je jeden ze zdrojových registrů totožný s registrem cílovým, odpovídá to příkazu:

if (condition) cíl = zdroj1 nebo zdroj2;

Kromě instrukce SEL existuje i instrukce SELN neboli (Conditional) Select-Not s opačně chápanou podmínkou.

Poznámka: podobně koncipované instrukce nalezneme i u mikroprocesorů s architekturou AArch64, zde se ovšem tyto instrukce jmenují CSEL a CSINV.

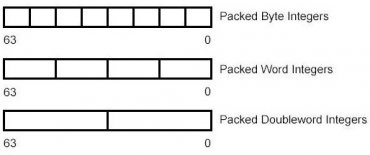

14. SIMD neboli operace s krátkými vektory

Všechny základní aritmetické a logické instrukce jsou určeny pro zpracování dvou 32bitových vstupních operandů s taktéž 32bitovým výsledkem. Ovšem u některých instrukcí podporují jádra TriCore i „vektorové“ zpracování, přičemž vektor může obsahovat buď dva šestnáctibitové prvky či čtyři prvky osmibitové (se znaménkem či bez znaménka). Příkladem použití může být zpracování signálů (výstupem A/D převodníků bývají osmibitové, desetibitové či právě šestnáctibitové hodnoty), práce s rastrovými obrázky (což pro TriCore ovšem není typický příklad použití) apod.

Obrázek 2: Typy vektorů, s nimiž pracují například procesory Intel. U jader TriCore je šířka dat poloviční, takže i počet prvků vektorů je poloviční.

Vybrané instrukce podporující práci s vektory mohou používat prefixy .B, .H, .BU a .HU pro rozlišení, zda jsou operandy osmibitové (Byte) či šestnáctibitové (Half-word) a taktéž pro rozlišení mezi operací s bezznaménkovými či znaménkovými operandy. Taktéž je možné zvolit, zda se například operace součtu bude provádět s přetečením či se saturací. Speciálním případem jsou DSP operace MUL.H/MULR.H/MULM.H pracující s vektory obsahujícími dva šestnáctibitové operandy. Jedná se o dodatkové instrukce k DSP instrukcím popsaným v jedenácté kapitole.

Obrázek 3: Vektorové operace.

15. Odkazy na Internetu

- Q (number format)

https://en.wikipedia.org/wiki/Q_%28number_format%29 - TriCore Architecture & Core

http://www.infineon.com/cms/en/product/microcontroller/32-bit-tricore-tm-microcontroller/tricore-tm-architecture-and-core/channel.html?channel=ff80808112ab681d0112ab6b73d40837 - TriCoreTM V1.6 Instruction Set: 32-bit Unified Processor Core

http://www.infineon.com/dgdl/tc_v131_instructionset_v138.pdf?fileId=db3a304412b407950112b409b6dd0352 - TriCore v2.2 C Compiler, Assembler, Linker Reference Manual

http://tasking.com/support/tricore/tc_reference_guide_v2.2.pdf - Infineon TriCore (Wikipedia)

https://en.wikipedia.org/wiki/Infineon_TriCore - C166®S V2 Architecture & Core

http://www.infineon.com/cms/en/product/microcontroller/16-bit-c166-microcontroller/c166-s-v2-architecture-and-core/channel.html?channel=db3a304312bef5660112c3011c7d01ae - Memory segmentation

https://en.wikipedia.org/wiki/Memory_segmentation - Bus mastering

https://en.wikipedia.org/wiki/Bus_mastering - ST10 16-bit MCUs

http://www.st.com/en/microcontrollers/st10–16-bit-mcus.html?querycriteria=productId=LN1111 - XC800 family

https://en.wikipedia.org/wiki/XC800_family - C166 (stránky společnosti Infineon)

https://www.infineon.com/cms/en/product/microcontroller/16-bit-c166-microcontroller/channel.html?channel=ff80808112ab681d0112ab6b2eaf0759#ispnTab3 - C166 Family

https://en.wikipedia.org/wiki/C166_family - Permanent Magnet Synchronous Motor

https://en.wikipedia.org/wiki/Synchronous_motor#Permanent_magnet_motors - Implementing field oriented control of a brushless DC motor

http://www.eetimes.com/document.asp?doc_id=1279321 - Vector control (motor)

https://en.wikipedia.org/wiki/Vector_control_(motor) - Motorola DSP56k

https://www.rockbox.org/wiki/MotorolaDSP56k - Motorola 56000 (Wikipedia)

http://en.wikipedia.org/wiki/Motorola_56000 - Using the Motorola DSP56002EVM for Amateur Radio DSP Projects

http://www.johanforrer.net/EVM/article.html - The Atari Falcon030 „Personal Integrated Media System“

http://www.atarimuseum.com/computers/16bits/falcon030.html - Turtle Beach Corporation (stránky společnosti)

http://www.turtlebeach.com/ - Turtle Beach Corporation (Wikipedia)

https://en.wikipedia.org/wiki/Turtle_Beach_Corporation - Atari Falcon 030 DSP 3D engine test

http://www.digiti.info/video/WHQwMjNRaExfLWs=/atari_falcon030_dsp_3d_engine_test - Atari Falcon030 (německy)

http://www.maedicke.de/atari/hardware/falcon.htm - Old-computers.com: Atari Falcon030

http://www.old-computers.com/museum/computer.asp?c=125&st=1 - Atari Falcon030 (Wikipedia)

http://en.wikipedia.org/wiki/Atari_Falcon - Past and current projects (including Falcon stuff)

http://os.inf.tu-dresden.de/~nf2/projects/projects.html - Atari Falcon 030: The Case For The Defence

http://www.soundonsound.com/sos/1994_articles/sep94/atarifalcon.html - DaVinci processor family

http://www.ti.com/general/docs/datasheetdiagram.tsp?genericPartNumber=TMS320DM365&diagramId=64193 - Texas Instruments DaVinci

https://en.wikipedia.org/wiki/Texas_Instruments_DaVinci - TMS320DM6446 (DaVinci)

http://www.ti.com/product/tms320dm6446 - Digital Media Video Processors (TI)

http://www.ti.com/lsds/ti/processors/dsp/media_processors/davinci/products.page# - TI Wiki

http://processors.wiki.ti.com/index.php/Main_Page - C5000 ultra-low-power DSP

http://www.ti.com/lsds/ti/processors/dsp/c5000_dsp/overview.page - OMAP (Wikipedia)

https://en.wikipedia.org/wiki/OMAP - OMAP – TI Wiki

http://processors.wiki.ti.com/index.php/OMAP - Why OMAP can't compete in smartphones

http://www.eetimes.com/author.asp?section_id=40&doc_id=1286602 - Applications Processors – The Heart of the Smartphone

http://www.engineering.com/ElectronicsDesign/ElectronicsDesignArticles/ArticleID/5791/Applications-Processors-The-Heart-of-the-Smartphone.aspx - TI cuts 1,700 jobs in OMAP shift

http://www.eetimes.com/document.asp?doc_id=1262782 - VLIW: Very Long Instruction Word: Texas Instruments TMS320C6×

http://www.ecs.umass.edu/ece/koren/architecture/VLIW/2/ti1.html - An Introduction To Very-Long Instruction Word (VLIW) Computer Architecture

Philips Semiconductors - VLIW Architectures for DSP: A Two-Part Lecture (PDF, slajdy)

http://www.bdti.com/MyBDTI/pubs/vliw_icspat99.pdf - Very long instruction word (Wikipedia)

https://en.wikipedia.org/wiki/Very_long_instruction_word - A VLIW Approach to Architecture, Compilers and Tools

http://www.vliw.org/book/ - VEX Toolchain (VEX = VLIW Example)

http://www.hpl.hp.com/downloads/vex/ - Elbrus (computer)

https://en.wikipedia.org/wiki/Elbrus_%28computer%29 - Super Harvard Architecture Single-Chip Computer

https://en.wikipedia.org/wiki/Super_Harvard_Architecture_Single-Chip_Computer - Digital Signal Processors (stránky TI)

http://www.ti.com/lsds/ti/processors/dsp/overview.page - C674× Low Power DSP (stránky TI)

http://www.ti.com/lsds/ti/processors/dsp/c6000_dsp/c674×/overview.page - TMS320C30 (stránky TI)

http://www.ti.com/product/tms320c30 - TMS320C6722B

http://www.ti.com/product/tms320c6722b/description - Introduction to DSP

http://www.ti.com/lit/wp/spry281/spry281.pdf - The Evolution of TMS (Family of DSPs)

http://www.slideshare.net/moto_modx/theevo1 - Datasheet k TMS32010

http://www.datasheetarchive.com/dlmain/49326c32a52050140abffe6f0ac4894aa09889/M/TMS32010 - 1979: Single Chip Digital Signal Processor Introduced

http://www.computerhistory.org/siliconengine/single-chip-digital-signal-processor-introduced/ - The TMS32010. The DSP chip that changed the destiny of a semiconductor giant

http://www.tihaa.org/historian/TMS32010–12.pdf - Texas Instruments TMS320 (Wikipedia)

https://en.wikipedia.org/wiki/Texas_Instruments_TMS320 - Great Microprocessors of the Past and Present: Part IX: Signetics 8×300, Early cambrian DSP ancestor (1978):

http://www.cpushack.com/CPU/cpu2.html#Sec2Part9 - Great Microprocessors of the Past and Present (V 13.4.0)

http://jbayko.sasktelwebsite.net/cpu.html - Introduction to DSP – DSP processors:

http://www.bores.com/courses/intro/chips/index.htm - The Scientist and Engineer's Guide to Digital Signal Processing:

http://www.dspguide.com/ - Digital signal processor (Wikipedia EN)

http://en.wikipedia.org/wiki/Digital_signal_processor - Digitální signálový procesor (Wikipedia CZ)

http://cs.wikipedia.org/wiki/Digitální_signálový_procesor - Digital Signal Processing FAQs

http://dspguru.com/dsp/faqs - Reprezentace numerických hodnot ve formátech FX a FP

http://www.root.cz/clanky/fixed-point-arithmetic/ - IEEE 754 a její příbuzenstvo: FP formáty

http://www.root.cz/clanky/norma-ieee-754-a-pribuzni-formaty-plovouci-radove-tecky/ - Čtyři základní způsoby uložení čísel pomocí FX formátů

http://www.root.cz/clanky/binarni-reprezentace-numerickych-hodnot-v-fx-formatu/ - Základní aritmetické operace prováděné v FX formátu

http://www.root.cz/clanky/zakladni-aritmeticke-operace-provadene-ve-formatu-fx/ - Aritmetické operace s hodnotami uloženými ve formátu FP

http://www.root.cz/clanky/aritmeticke-operace-s-hodnotami-ve-formatu-plovouci-radove-carky/ - FIR Filter FAQ

http://dspguru.com/dsp/faqs/fir - Finite impulse response (Wikipedia)

http://en.wikipedia.org/wiki/Finite_impulse_response - DSPRelated

http://www.dsprelated.com/ - Addressing mode (Wikipedia)

https://en.wikipedia.org/wiki/Addressing_mode - Orthogonal instruction set

https://en.wikipedia.org/wiki/Orthogonal_instruction_set - TI 16-bit and 32-bit microcontrollers

http://www.ti.com/lsds/ti/microcontrollers16-bit32-bit/overview.page - TMS 32010 Assembly Language Programmer's Guide (kniha na Amazonu)

https://www.amazon.com/32010-Assembly-Language-Programmers-Guide/dp/0904047423 - COSC2425: PC Architecture and Machine Language, PC Assembly Language

http://www.austincc.edu/rblack/courses/COSC2425/index.html