Obsah

1. Podpora instrukcí typu SIMD na mikroprocesorech ARM

2. Nové instrukce určené pro podporu zpracování signálů (DSP)

4. Nová sada pracovních registrů používaných v jednotce NEON

5. Instrukce typu Load & Store

6. Podpora SIMD instrukcí ve vyšších programovacích jazycích

7. Podpora SIMD instrukcí pro „hardcore“ programátory

8. Interní funkce (intrinsic) nabízené překladačem C a C++

1. Podpora instrukcí typu SIMD na mikroprocesorech ARM

Jak již bylo řečeno v perexu článku, budeme se v dnešní části seriálu o architekturách počítačů zabývat popisem způsobu implementace SIMD instrukcí na mikroprocesorech ARM. Připomeňme si, že SIMD instrukce, tj. instrukce, pomocí nichž se aplikuje jedna operace na vektor dat (většinou se jedná o dvojici vektorů pevné délky), začaly být postupně zaváděny na různých typech mikroprocesorů, ať již se jedná o mikroprocesory s architekturou CISC (rozšíření instrukční sady MMX, 3DNow!, SSE, SSE2 atd. na platformě 80×86), nebo naopak o mikroprocesory s architekturou RISC (rozšíření instrukční sady MDMX/MaDMaX a MIPS-3D na procesorech MIPS, instrukční sada MAX-1 na mikroprocesorech HP PA-RISC, sada VIS na mikroprocesorech SPARC atd.). Dokonce se dá s trochou nadsázky říci, že téměř každý výrobce mikroprocesorů (snad s výjimkou výrobců osmibitových mikrořadičů) dříve či později nabídl rozšíření původní instrukční sady o instrukce typu SIMD a mikroprocesory ARM v tomto ohledu nejsou výjimkou.

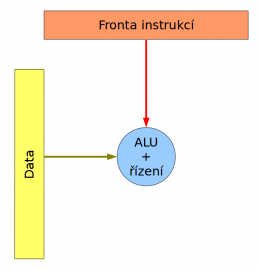

Obrázek 1: Schéma systému (mikroprocesoru) patřícího do kategorie SISD. Jedna instrukce je vykonána pouze nad skalárními operandy.

Instrukce SIMD představují pouze jednou z možností zvýšení výpočetního výkonu mikroprocesorů. Další variantou jsou – podle používané Flynnovy klasifikace sekvenčních a paralelních systémů – instrukce/architektura MISD využívaná ve specializovaných aplikacích či nejobecnější architektura MIMD. Ve více než padesátileté historii vývoje výpočetní techniky se již objevily všechny čtyři možné kombinace instrukčního a datového paralelismu. Viz též následující tabulka:

| Zkratka klasifikace | Anglický význam zkratky | Využití systémů s danou klasifikací |

|---|---|---|

| SISD | Single Instruction Stream, Single Data | klasická architektura pro procesory CISC a RISC |

| SIMD | Single Instruction Stream, Multiple Data | vektorové procesory, GPU, procesory s instrukční sadou SSE/MMX… |

| MISD | Multiple Instructions Stream, Single Data Stream | poměrně speciální případy, řídicí počítače raketoplánů (Space Shuttle) |

| MIMD | Multiple Instructions Stream, Multiple Data Stream | Connection Machine, transputery, symetrické multiprocesory |

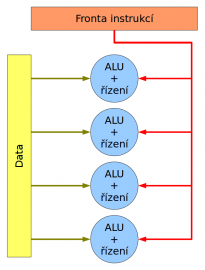

Obrázek 2: Schéma systému patřícího do kategorie SIMD. Jedna instrukce pracuje s vektorem či vektory dat.

Užitečné odkazy na vybrané předchozí části tohoto seriálu:

- Vektorové procesory aneb další pokus o zvýšení výpočetního výkonu počítačů

http://www.root.cz/clanky/vektorove-procesory-aneb-dalsi-pokus-o-zvyseni-vypocetniho-vykonu-pocitacu/ - SIMD instrukce využívané v moderních mikroprocesorech řady x86

http://www.root.cz/clanky/simd-instrukce-vyuzivane-v-modernich-mikroprocesorech-rady-x86/ - SIMD instrukce v moderních mikroprocesorech řady x86 (2.část: SSE)

http://www.root.cz/clanky/simd-instrukce-v-modernich-mikroprocesorech-rady-x86–2-cast-sse/ - SIMD instrukce v moderních mikroprocesorech řady x86 (3.část: SSE2)

http://www.root.cz/clanky/simd-instrukce-v-modernich-mikroprocesorech-rady-x86–3-cast-sse2/ - Instrukce typu SIMD na mikroprocesorech RISC

http://www.root.cz/clanky/instrukce-typu-simd-na-mikroprocesorech-risc/ - Instrukce typu SIMD na mikroprocesorech RISC (2. část)

http://www.root.cz/clanky/instrukce-typu-simd-na-mikroprocesorech-risc-2-cast/ - Instrukce typu SIMD na mikroprocesorech RISC (3.část – MIPS-3D a VIS)

http://www.root.cz/clanky/instrukce-typu-simd-na-mikroprocesorech-risc-3-cast-mips-3d-a-vis/

2. Nové instrukce určené pro podporu zpracování signálů (DSP)

V předchozí části tohoto seriálu jsme se zaměřili na popis instrukční sady VFP neboli Vector Floating Point. Jedná se o instrukční sadu podporovanou některými jádry ARM, v níž jsou programátorům nabídnuty instrukce pro provádění různých aritmetických a logických operací s vektory čísel reprezentovaných v systému plovoucí řádové čárky (FP – Floating Point). Na první pohled by se tedy mohlo zdát, že se jedná o jednu z mnoha aplikací architektury SIMD, ve skutečnosti se ovšem v případě VFP vektory zpracovávají sekvenčně. To například znamená, že součet dvou osmiprvkových vektorů realizovaný instrukcí VADD používá tu samou FP-sčítačku a prvky vektorů jsou tedy sečítány postupně (ušetří se však čas na načtení a dekódování zbylých sedmi instrukcí). Mikroprocesory ARM se ovšem začaly využívat i v oblasti zpracování signálů, kde se většinou pracuje s celočíselnými údaji (integer), popř. s čísly s pevnou řádovou čárkou (fixed point), s nimiž se v aritmeticko-logické jednotce pracuje podobným způsobem jako s celými čísly.

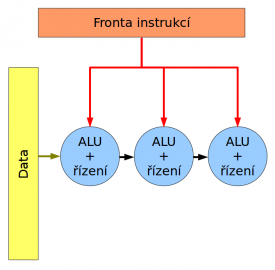

Obrázek 3: Schéma systému patřícího do kategorie MISD.

Právě pro oblast zpracování signálů (DSP) a taktéž pro implementaci multimediálních aplikací bylo určeno rozšíření pro DSP operace v mikroprocesorech s jádrem ARMv5TE. Nové instrukce byly využitelné například při kódování a dekódování videa, při zpracování zvukového signálu (včetně zvukové syntézy), práci s rastrovými obrazy (image processing) atd. Instrukce typu Load & Store mohly pracovat s registrovými páry, zavedeny byly nové adresovací režimy, aritmetika se saturací (tj. bez přetečení) a taktéž instrukce typu „multiply and accumulate (MAC)“ 16×16 bitů a 32×16 bitů, které mohly být v instrukční pipeline vykonány v rozmezí jednoho taktu (v jejich průběhu se tedy mohly začít zpracovávat další instrukce). Uvádí se, že při zpracování signálů byla výkonnost nových instrukcí v jádrech ARMv5TE dvakrát až třikrát vyšší, než při použití „běžných“ jader ARMv5 (samozřejmě za předpokladu ruční optimalizace kódu, což ostatně až na některé výjimky platí dodnes).

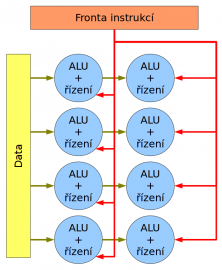

Obrázek 4: Schéma systému patřícího do kategorie MIMD.

3. Architektura NEON

Možná to nemusí být na první pohled patrné, ale instrukce typu SIMD prováděné (především) s jedním či dvěma vektory celých čísel vlastně velmi dobře zapadají do filozofie, na které jsou postaveny mikroprocesory ARM – tato filozofie je založena na dosažení optimálního výpočetního výkonu za předpokladu, že se nebude zbytečně zvětšovat počet tranzistorů a tím pádem ani spotřeba (příkon) čipu. Podívejme se například na typickou operaci prováděnou při zpracování rastrového obrazu – zvýšení jasu celého obrazu o nějaký offset n. V případě, že jsou pixely uloženy v barvovém modelu RGB s osmi bity rezervovanými pro každou barvovou složku, znamená to, že se součet s číslem n musí provést width×height×3 krát (pro jednoduchost nyní pomiňme nutnost provádět součet se saturací – bez přetečení – i fakt, že se touto operací může změnit barevný tón obrazu).

Obrázek 5: Zdrojový rastrový obrázek (známá fotografie Lenny), který tvoří zdroj pro jednoduchý konvoluční (FIR) filtr, jenž zvyšuje hodnoty pixelů o pevně zadanou konstantu (offset).

Ovšem při zmíněném provádění součtu width×height×3 krát je 32bitová aritmeticko-logická jednotka využita pouze z jedné čtvrtiny, protože výsledek součtu bude pouze osmibitový (devátý bit supluje přetečení). Pokud by se v tomto případě použily SIMD instrukce provádějící součet čtyřprvkového vektoru osmibitových čísel (dohromady tedy 32bitového slova), byla by aritmeticko-logická jednotka zcela vytížena, ovšem celkový počet operací součtu by se snížil na pouhou čtvrtinu – to ovšem za předpokladu, že aritmeticko-logická jednotka bude relativně snadno (= s malým počtem nových tranzistorů) upravena na možnost sečíst dvouprvkové či čtyřprvkové vektory.

Obrázek 6: Pokud je pro přičtení offsetu použita operace součtu se zanedbáním přenosu (carry), tj. když se počítá systémem „modulo N“, dochází při překročení maximální hodnoty pixelu (čistě bílá barva) k jasně viditelným chybám.

Není tedy divu, že se instrukce typu SIMD postupně na platformě mikroprocesorů ARM rozšiřovaly. Po již zmíněném jádru ARMv5TE bylo další rozšíření o instrukce SIMD použito u některých jader ARMv6, kde začaly být podporovány například operace typu MAC 32×32 bitů se zlomky (resp. s bitovým posunem mezivýsledků), aritmetické operace prováděné nad dvojicí registrů atd. Oproti ARMv5TE byla výkonnost multimediálních aplikací přibližně dvojnásobná. Ovšem mnohem zajímavější je technologie NEON, která dosti revolučním způsobem mění i konfiguraci interních bloků mikroprocesorů, zavádí přibližně 100 nových instrukcí SIMD a taktéž rozšiřuje původní sadu pracovních registrů o 32 nových registrů, z nichž každý má šířku 64 bitů. Při návrhu technologie NEON se její tvůrci zaměřili na implementaci těch operací, které se v praxi skutečně provádí, takže je například poměrně snadné (a především efektivní) pracovat s různými formáty rastrových bitmap, zpracovávat 16bitové zvukové vzorky při práci se stereo signálem atd.

Obrázek 7: Při použití operace součtu se saturací sice taktéž dojde ke ztrátě informace (vzniknou oblasti s pixely majícími hodnotu 255), ovšem viditelná chyba je mnohem menší, než na předchozím obrázku.

4. Nová sada pracovních registrů používaných v jednotce NEON

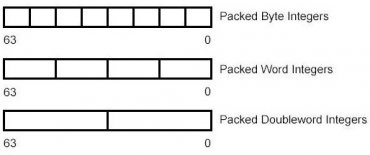

V rámci technologie NEON byla původní sada registrů mikroprocesorů ARM rozšířena o 32 nových 64bitových registrů nazvaných d0 až d31. Tyto registry se mohou u některých instrukcí sdružovat do párů a vytvářet tak sadu 128bitových registrů nazvaných q0 až q15 (d0+d1 vytvoří registr q0 atd.). V případě, že daný mikroprocesor implementuje jak sadu VFP, tak i NEON, mohou být registry mezi sebou sdíleny, což může komplikovat současné provádění „vektorových“ operací s FP hodnotami a s hodnotami celočíselnými. 64 či 128bitové registry mohou podle typu prováděné instrukce obsahovat operace různých typů. Technologie NEON podporuje vektory obsahující osmibitové hodnoty (typicky například barvové složky pixelů), 16bitové hodnoty (zvukové vzorky), 32bitové hodnoty i hodnoty 64bitové – podle potřeby se znaménkem (signed) i bez znaménka (unsigned). Kromě toho mohou některé instrukce pracovat i s 32bitovými hodnotami reprezentovanými v systému plovoucí řádové čárky (jedná se o standardní datový typ float/single).

Obrázek 8: Vybrané typy vektorů, s nimiž pracují instrukce NEON.

Důvodů pro zavedení nových registrů existovalo několik. Samozřejmě platí, že čím více obecných registrů je k dispozici, tím lehčí práci mají překladače a tím méně času musí mikroprocesor čekat na pomalou paměť RAM, popř. na o něco rychlejší vyrovnávací paměť. Ovšem závažnějším důvodem je to, že instrukce zavedené v technologii NEON jsou v jednotce/modulu NEON zpracovávány odděleně od ostatních instrukcí procesorů ARM. Vše funguje tak, že je každá instrukce načtena do klasické pipeline procesorů ARM a ve chvíli, kdy se rozpozná, že se jedná o SIMD instrukci, je tato instrukce vložena do krátké šestnáctiprvkové fronty instrukcí (délka fronty se liší podle typu jádra) a z hlediska procesoru ARM je takto „odkloněná“ instrukce vlastně ihned dokončena, takže jádro ARM může ihned pokračovat v provádění dalších běžných instrukcí. Jednotka NEON postupně vybírá instrukce z již zmíněné 16prvkové fronty a provádí je s využitím své sady registrů zcela odděleně od jádra ARM (mimochodem – pipeline u jednotky NEON má typicky deset řezů a některé jednotky jsou zdvojené či dokonce ztrojené, aby se dosáhlo vyššího výpočetního výkonu). Tato kooperace a paralelní běh se zastaví ve chvíli, kdy je fronta jednotky NEON zaplněná, popř. se musí vyměnit data mezi pracovními registry jádra ARM a registry jednotky NEON.

5. Instrukce typu Load & Store

Již z mnoha předchozích částí tohoto seriálu víme, že mikroprocesory s architekturou RISC jsou typické mj. i tím, že se veškeré operace provádí s hodnotami uloženými v pracovních registrech a práce s operační pamětí je omezena pouze na instrukce typu Load & Store. Ve skutečnosti však mnohdy právě tyto instrukce provádí ještě nějaké předzpracování dat, popř. konverzi dat při ukládání. Typicky se u mnoha RISCových procesorů může provádět znaménkové rozšíření načítaného operandu (v případě, že bitová šířka operandu je menší, než šířka pracovních registrů). Ovšem u technologie NEON byly možnosti instrukcí Load & Store poměrně významně rozšířeny, protože umožňují provádět načtení či uložení vektorů s tím, že prvky vektorů mohou být různým způsobem přeskládány či konvertovány. Nejprve si řekněme, že pro načtení vektorů (několika prvků) do vybraných registrů se používá instrukce VLD (Vector LoaD) a pro zpětné uložení vektoru do paměti se používá instrukce VST (Vector STore).

Podívejme se nyní na možnosti, které programátorům nabízí instrukce VLD. Ta se v assembleru zapisuje podle následujícího vzoru:

VLD interleave.bits{seznam registrů}, adresa

V tomto vzoru je pouze mnemotechnická zkratka instrukce VLD neměnná. Další (proměnné) údaje mají tento význam:

- Hodnota interleave může být nastavena na 1, 2, 3 či 4. Pomocí této hodnoty se určuje „mezera“ mezi dvěma prvky v paměti, které mají být ve výsledném vektoru uloženy za sebou. Při použití VLD 1 se prvky do vektoru načtou tak, jak jsou uloženy v paměti, instrukce VLD 2 se používá tehdy, pokud jsou v paměti uloženy zvukové vzorky v systému levý kanál:pravý kanál (zvukové vzorky), instrukce VLD 3 se využívá u rastrových obrázků ve formátu RGB (dojde k extrakci barvových složek do tří vektorů) a konečně instrukce VLD 4 například u obrázků ve formátu RGBA či ARGB.

- Hodnota bits určuje počet bitů rezervovaných pro každý prvek vektoru. Podporované hodnoty jsou 8, 16 a 32.

- V seznamu registrů může být umístěn jeden až čtyři pracovní registry d0 až d31, v závislosti na hodnotách interleave a bits (zápis vypadá takto: {d0, d1}). Při použití VLD 1 se načtou prvky do čtyř specifikovaných registrů (neprovádí se žádné prohazování prvků), při VLD 2 se používá dvojice registrů či čtveřice registrů, při VLD 3 trojice pracovních registrů (první prvek bude načten do prvního registru, druhý do registru druhého, třetí do třetího, čtvrtý opět do prvního atd.) a při VLD 4 se používají čtyři pracovní registry.

- Zbývá nám vysvětlit význam adresy. Zde se většinou používá některý pracovní registr ARM, například [r0] (pracovní registry NEON většinou adresu neobsahují). Hodnotu tohoto registru lze buď pouze beze změny využít, nebo ji lze i inkrementovat a to buď o počet skutečně načtených bajtů (nikoli o jedničku – to by nemělo žádný praktický význam), nebo ji lze zvýšit o hodnotu registru Rm, který může být taktéž součástí instrukce. Tato druhá možnost se používá například tehdy, pokud se prochází dvourozměrným polem po sloupcích a nikoli po řádcích (co to udělá se strukturou vyrovnávací paměti je věc druhá).

Ukažme si pro ilustraci dvě instrukce:

; načtení čtyř 16bitových elementů do prvního registru (vektoru) ; načtení čtyř 16bitových elementů do registru druhého ; proložení 1:1 VLD2.16 ; načtení dvou 32bitových elementů do prvního registru (vektoru) ; načtení dvou 32bitových elementů do registru druhého ; proložení 1:1 VLD2.32

Nyní si ukážeme trošku složitější příklad – převod rastrového obrazu z formátu RGB do formátu BGR, tj. prohození hodnoty R a B v každém pixelu. Tuto relativně často prováděnou operaci (viz rozdílné formáty framebufferu) lze snadno provést pro osmici sousedních pixelů společně:

; registr r0 ukazuje na prvni bajt

; pixelu ulozeneho ve formatu BGR

; nacteni RGB hodnot osmi pixelu

; barvove slozky jsou rozdeleny

; do trech pracovnich registru d0, d1 a d2

; + zmena adresy

vld3.8 {d0, d1, d2}, [r0]!

; prohozeni barvovych slozek B a R

; (prohozeni vektoru ulozenych v d0 a d2

; nezavisle na internim formatu)

vswp d0, d2

; registr r1 ukazuje na prvni bajt

; pixelu ulozeneho ve formatu RGB

; zpetne slozeni barvovych slozek

; osmi pixelu, ktere byly rozdeleny

; + zmena adresy

vst3.8 {d0, d1, d2}, [r1]!

6. Podpora SIMD instrukcí ve vyšších programovacích jazycích

Nové instrukce zavedené v rámci technologie NEON lze samozřejmě využívat především přímo v assembleru, což je sice ta nejobtížnější varianta, na druhou stranu však má programátor v tomto případě možnost přímo a do všech podrobností ovlivnit výslednou podobu programu. Ovšem naprostá většina programového kódu je v současnosti vytvářena ve vyšších programovacích jazycích. Z tohoto důvodu musí existovat nějaká možnost, jak tyto nové instrukce ve vyšších programovacích jazycích využívat. Z hlediska programátora je nejjednodušší možností využít již existující odladěné a optimalizované knihovny implementované právě s pomocí SIMD instrukcí, což je většinou ideální řešení v případech, kdy tyto knihovny již obsahují implementaci časově nejnáročnějších částí programů. Mezi takové knihovny patří v případě mikroprocesorů ARM a technologie NEON například knihovna OpenMAX DL, v níž jsou implementovány různé zvukové i video kodeky: části algoritmů pro komprimaci a dekomprimaci pomocí JPEG (rastrové obrazy), MP3 (zvuk), H.264 (AV kodek), MPEG-4 (taktéž AV kodek) atd.

Kromě těchto algoritmů či jejich částí jsou v knihovně OpenMAX DL implementovány i funkce určené pro filtraci a zpracování signálů, především FIR, IIR (číslicové filtry s konečnou a nekonečnou impulsní odezvou) a FFT (rychlá Fourierova transformace). SIMD instrukce byly použity i při optimalizaci známé knihovny Cairo pro procesory ARM, kde se například podařilo zrychlit některé operace s rastrovým obrazem (alpha blending) až osmkrát v porovnání se „sekvenčním“ řešením (v případě Cairo se však podle mých informací veškeré optimalizace týkaly pouze úpravy některých funkcí pro práci s rastrovým obrazem; nešlo tedy o optimalizaci většiny funkcí, které jsou v této poměrně rozsáhlé knihovně implementovány).

Užitečné odkazy:

- Porovnání výkonnosti knihovny Cairo při SW renderingu:

http://ssvb.github.com/2012/05/04/xorg-drivers-and-software-rendering.html - Další porovnání výkonnosti SW renderingu:

http://people.freedesktop.org/~siamashka/files/20100216/pixman-0.17.6/ - Ne10: A New Open Source Library to Accelerate your Applications with NEON:

http://blogs.arm.com/software-enablement/703-ne10-a-new-open-source-library-to-accelerate-your-applications-with-neon/ - Khronos Standards (odkazy na implementované knihovny):

http://www.arm.com/community/multimedia/standards-apis.php

7. Podpora SIMD instrukcí pro „hardcore“ programátory

Další možnost využití instrukcí typu SIMD i z vyšších programovacích jazyků spočívá v takzvané automatické „vektorizaci“. Překladače jazyků C a C++ (GCC u procesorů ARM) totiž v některých případech dokážou rozpoznat, že je možné nějakou programovou smyčku provádět nikoli čistě sekvenčně, ale s využitím operací prováděných nad vektory. Programátor však musí v těchto případech překladači vhodným způsobem „napovědět“, například tak, že přímo v programu naznačí, že počet cyklů ve smyčce bude za všech okolností dělitelný čtyřmi či osmi atd. To nemusí být vždy úplně jednoduché, už jen z toho důvodu, že jazyky C a C++ nepodporují zápis metadat do programu (v Javě by to bylo umožněno s využitím anotací). Podívejme se na následující příklad, kde je při zápisu počítané smyčky typu for překladači céčka naznačeno, že počet opakování smyčky bude vždy dělitelný čtyřmi, resp. že poslední dva bity horní meze počitadla budou nulové (hodnota n je maskována číslem, které má ve svých dvou nejnižších bitech nuly):

void add_offset_to_vector(int * __restrict px, int * __restrict py, int n, int offset)

{

unsigned int i;

for (i=0; i < (n & ~3); i++)

{

px[i] = py[i] + offset;

}

}

8. Interní funkce (intrinsic) nabízené překladačem C a C++

Automatická „vektorizace“ popsaná v předchozí kapitole však nedokáže (alespoň v současnosti) využít celého potenciálu technologie NEON. Z tohoto důvodu mohou programátoři v případě potřeby zavolat přímo z programů psaných v C či C++ takzvané interní (intrinsic) funkce, tj. funkce, které jsou překladačem spravovány speciálním způsobem. Jejich použití se sice podobá volání běžné funkce, ve skutečnosti se však jedná o makro, které překladač vhodným způsobem expanduje do použití některé instrukce zavedené v technologii NEON. Příklad použití intrinsic funkce je ukázán níže na volání instrukce pro součet dvou vektorů. Ze zápisu je patrné, že sečítané vektory (oba představované jednou strukturou) obsahují 32bitová čísla bez znaménka (unsigned) a že tyto vektory jsou uložené ve 128bitovém registru qx (ten je, jak již víme, sestaven z registrových párů dn a d(n+1):

#include <arm_neon.h>

uint32x4_t double_elements(uint32x4_t input)

{

return(vaddq_u32(input, input));

}

Seznam všech podporovaných intrinsic funkcí lze nalézt například na této adrese:

http://gcc.gnu.org/onlinedocs/gcc/ARM-NEON-Intrinsics.html

Poslední možností je samozřejmě již zmíněné využití assembleru, a to buď přímo (část funkcí bude zapsaná v assembleru a překládaná do objektového kódu pomocí GAS) nebo s využitím inline assembleru zapisovaného přímo do těla céčkových funkcí či C++ových metod. Zde již samozřejmě dochází ke ztrátě přenositelnosti, která v předchozích případech vlastně zůstávala zachována (i ona zmíněná instrukce vaddq_u32 by totiž mohla být pro účely přenositelnosti implementována jako běžné makro či přímo céčková funkce při překladu na těch mikroprocesorech, které nejsou technologií NEON vybaveny).

9. Odkazy na Internetu

- The VFP architecture

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0056d/Bcfibfha.html - NEON

http://www.arm.com/products/processors/technologies/neon.php - ARM Floating Point Accelerator (ARM FPA)

http://vswww.kaist.ac.kr/ver4.0/index.php/research/past-research/arm-fpa.html - Coding for NEON – Part 1: Load and Stores

http://blogs.arm.com/software-enablement/161-coding-for-neon-part-1-load-and-stores/ - Coding for NEON – Part 2: Dealing With Leftovers

http://blogs.arm.com/software-enablement/196-coding-for-neon-part-2-dealing-with-leftovers/ - Coding for NEON – Part 3: Matrix Multiplication

http://blogs.arm.com/software-enablement/241-coding-for-neon-part-3-matrix-multiplication/ - Coding for NEON – Part 4: Shifting Left and Right

http://blogs.arm.com/software-enablement/277-coding-for-neon-part-4-shifting-left-and-right/ - DSP & SIMD

http://www.arm.com/products/processors/technologies/dsp-simd.php - Improving ARM Code Density and Performance

New Thumb Extensions to the ARM Architecture Richard Phelan - The ARM Processor Architecture

http://www.arm.com/products/processors/technologies/instruction-set-architectures.php - Thumb-2 instruction set

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0344c/Beiiegaf.html - Introduction to ARM thumb

http://www.eetimes.com/discussion/other/4024632/Introduction-to-ARM-thumb - ARM, Thumb, and ThumbEE instruction sets

http://www.keil.com/support/man/docs/armasm/armasm_CEGBEIJB.htm - An Introduction to ARM Assembly Language

http://dev.emcelettronica.com/introduction-to-arm-assembly-language - Processors – ARM

http://www.arm.com/products/processors/index.php - The ARM Instruction Set

http://simplemachines.it/doc/arm_inst.pdf - ARM Architecture (Wikipedia)

http://en.wikipedia.org/wiki/ARM_architecture - BBC BASIC

http://www.bbcbasic.co.uk/bbcbasic.html - BBC BASIC

http://mdfs.net/Software/BBCBasic/ - BBC BASIC (Z80) for the ZX Spectrum

http://mdfs.net/Software/BBCBasic/Spectrum/ - BBC BASIC (Wikipedia CZ)

http://en.wikipedia.org/wiki/BBC_BASIC - MIPS-3D® ASE

http://www.mips.com/products/architectures/mips-3d-ase/ - An introduction to SPARC's SIMD offerings

http://mikeburrell.wordpress.com/2007/12/14/an-introduction-to-sparcs-simd-offerings/ - MIPS64TM Architecture for Programmers Volume IV-c: The MIPS-3DTM Application-Specific Extension to the MIPS64TM

http://www.weblearn.hs-bremen.de/risse/RST/docs/MIPS/MD00099–2B-MIPS3D64-AFP-01.11.pdf - Visual Instruction Set

http://www.enotes.com/topic/Visual_Instruction_Set - NEON

http://www.arm.com/products/processors/technologies/neon.php - Architecture and Implementation of the ARM Cortex-A8 Microprocessor

http://www.design-reuse.com/articles/11580/architecture-and-implementation-of-the-arm-cortex-a8-microprocessor.html - Multimedia Acceleration eXtensions (Wikipedia)

http://en.wikipedia.org/wiki/Multimedia_Acceleration_eXtensions - AltiVec (Wikipedia)

http://en.wikipedia.org/wiki/AltiVec - Visual Instruction Set (Wikipedia)

http://en.wikipedia.org/wiki/Visual_Instruction_Set - MAJC (Wikipedia)

http://en.wikipedia.org/wiki/MAJC - MDMX (Wikipedia)

http://en.wikipedia.org/wiki/MDMX - MIPS Multiply Unit

http://programmedlessons.org/AssemblyTutorial/Chapter-14/ass14_3.html - Silicon Graphics Introduces Enhanced MIPS Architecture

http://bwrc.eecs.berkeley.edu/CIC/otherpr/enhanced_mips.html - MIPS-3D (Wikipedia)

http://en.wikipedia.org/wiki/MIPS-3D - MIPS Technologies, Inc. announces new MIPS-3D technology to provide silicon-efficient 3D graphics acceleration

http://www.design-reuse.com/news/2057/mips-mips-3d-technology-silicon-efficient-3d-graphics-acceleration.html - MIPS-3D Built-in Function (gcc.gnu.org)

http://gcc.gnu.org/onlinedocs/gcc/MIPS_002d3D-Built_002din-Functions.html - Baha Guclu Dundar:

Intel MMX, SSE, SSE2, SSE3/SSSE3/SSE4 Architectures - SSE (Streaming SIMD Extentions)

http://www.songho.ca/misc/sse/sse.html - Timothy A. Chagnon: SSE and SSE2

http://www.cs.drexel.edu/~tc365/mpi-wht/sse.pdf - Intel corporation: Extending the Worldr's Most Popular Processor Architecture

http://download.intel.com/technology/architecture/new-instructions-paper.pdf - SIMD architectures:

http://arstechnica.com/old/content/2000/03/simd.ars/ - Intel MMXTM Technology Overview

Intel corporation, 1996 - MultiMedia eXtensions

http://softpixel.com/~cwright/programming/simd/mmx.php - AMD K5 („K5“ / „5k86“)

http://www.pcguide.com/ref/cpu/fam/g5K5-c.html - Sixth Generation Processors

http://www.pcguide.com/ref/cpu/fam/g6.htm - Great Microprocessors of the Past and Present

http://www.cpushack.com/CPU/cpu1.html - Very long instruction word (Wikipedia)

http://en.wikipedia.org/wiki/Very_long_instruction_word - Tour of the Black Holes of Computing!: Floating Point

http://www.cs.hmc.edu/~geoff/classes/hmc.cs105…/slides/class02_floats.ppt - 3Dnow! Technology Manual

AMD Inc., 2000 - CPU design (Wikipedia)

http://en.wikipedia.org/wiki/CPU_design - Control unit (Wikipedia)

http://en.wikipedia.org/wiki/Control_unit - Cray History

http://www.cray.com/About/History.aspx?404;http://www.cray.com:80/about_cray/history.html - Cray Historical Timeline

http://www.cray.com/Assets/PDF/about/CrayTimeline.pdf - Computer Speed Claims 1980 to 1996

http://homepage.virgin.net/roy.longbottom/mips.htm - Superpočítače Cray

http://www.root.cz/clanky/superpocitace-cray/ - Superpočítače Cray (druhá část)

http://www.root.cz/clanky/superpocitace-cray-druha-cast/ - Superpočítače Cray (třetí část)

http://www.root.cz/clanky/superpocitace-cray-treti-cast/ - Superpočítače Cray (čtvrtá část)

http://www.root.cz/clanky/superpocitace-cray-ctvrta-cast/ - Superpočítače Cray (pátá část): architektura Cray X-MP

http://www.root.cz/clanky/superpocitace-cray-pata-cast-architektura-pocitace-cray-x-mp-a-jeho-pouziti-ve-filmovem-prumyslu/